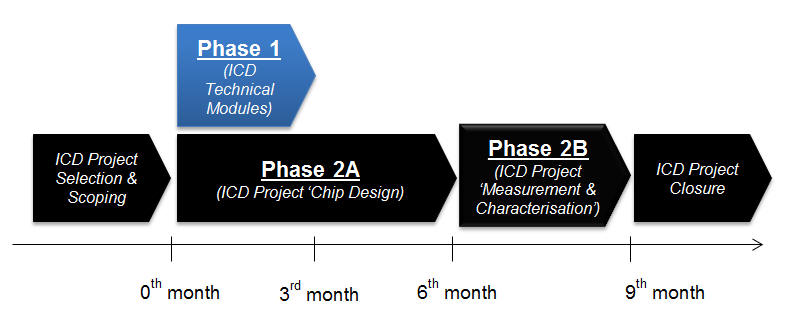

Phase 1 – Technical Modules

Phase 1 consist of 3 ICD–related technical modules of 40hrs

each, to be conducted concurrently with Phase 2A, the ‘Chip

Design’ phase. These modules would be rolled-out to complement

the implementation of the IC Design industrial project.

Design of Analog Integrated Circuit (IC) - 40 hrs

This course focuses on basic analog integrated circuit design.

It includes design and analysis of basic analog functional

module designs such as current mirrors, active load, biasing

circuits, voltage reference and operational amplifiers. This

course exposes trainees to fundamentals of semiconductor

processing, characteristics and implementation of passive and

active components, including electrical modelling and SPICE

simulation techniques. In the hands-on sessions, the trainees

will learn to design analog circuits based on a given

specifications. Through hands-on calculation and extensive

simulations, they will design the analog block.

Design of Radio Frequency Integrated Circuit (RFIC)

The course deals with the analysis and design of RF integrated

circuits, RF IC modelling, and provides a systematic view on RF

ICs. The course will handle the architectures and also

emphasizes circuit level designs with respect to CMOS VLSI

technologies. At the completion of the subject, trainees should

be able to appreciate the system considerations and the circuit

behaviours, understand the methodologies for the design and

modelling of RF integrated circuits, understand the design

considerations of RF integrated circuits and hence capable of

analysing and synthesising new RF architectures based on the

concept learned in the course, and understand the effects of the

parasitic parameters introduced from layout of a block of CMOS

circuit.

Design of Digital System Integrated Circuit (IC) with Verilog

HDL - 40 hrs

This course covers the use of Verilog HDL in high-level

synthesis of digital system designs. The language Verilog HDL as

well as how it is used for describing, modelling, simulating and

synthesizing various digital modules will be addressed. Verilog

HDL coding and synthesis issues on combinational and sequential

modules including Finite State Machine will be discussed. In the

hands-on sessions, the trainees will not only learn the language

through hands-on coding, synthesis and simulation of some

practical designs, but they will also synthesize and test the

designs with industrial software packages and FPGA devices.

WSQ Certified Associate Operations

Executive programme

Participants receiving the WDA subsidy will be

required to undertake an additional module within the WSQ

Certified Associate Operations Executive programme delivered by

any of WDA’s appointed WSQ external training providers. For more

information, please click

here.