Available online at www.sciencedirect.com

Sensors and Actuators A 119 (2005) 446-454

SENSORS ACTUATORS A PHYSICAL

www.elsevier.com/locate/sna

# Optimization of design and fabrication for micromachined true time delay (TTD) phase shifters

W. Palei, A.Q. Liu\*, A.B. Yu, A. Alphones, Y.H. Lee

School of Electrical and Electronic Engineering, Nanyang Technological University, Nanyang Avenue, Singapore 639798, Singapore

Received 4 August 2004; received in revised form 9 August 2004; accepted 1 October 2004 Available online 19 March 2005

#### Abstract

Distributed techniques have been widely employed as a solution to obtain wide band circuits at microwave and millimeter wave band. This paper presents five different designs for true-time delay (TTD) phase shifters that are based on characteristic impedance of 75, 65 and 50  $\Omega$  coplanar waveguide (CPW) distributed microelectromechanical systems (MEMS) transmission line (DMTL), which are loaded with different designs and number of shunt capacitive switches. The TTD phase shifters are fabricated on a 675  $\mu$ m high resistivity silicon (Si) wafer using surface micromachining process. The design operates up to Ku band with a measured return loss below -15 dB and an average loss of 2.3 dB/phase shift of 250° at 20 GHz. The TTD phase shifters have wide applications for high-performance of microwave and millimeter-wave integrated circuits.

© 2004 Published by Elsevier B.V.

Keywords: MEMS; Capacitive shunt switch; Distributed MEMS transmission line (DMTL); True time delay (TTD) phase shifter; Radio frequency (RF)

## 1. Introduction

Current development in radio frequency (RF) microelectromechanical systems (MEMS) has greatly improved the performance of the millimeter wave switches and phase shifters, which are essential for modern radar and telecommunication systems. Low loss and less measurable intermodulation distortion are two main advantages of MEMS over field effect transistor (FET) or p-i-n diodes [1]. As a result, RF MEMS concept has been successfully applied in the past few years to develop low loss RF switching devices and variable capacitors [2–4]. Most of these MEMS based switches can be fabricated directly with on quartz, glass and silicon substrates, which results in a relatively low-cost phased array antenna [5,6]. Although the switching speed of the MEMS devices may not be comparable to the FET or p-i-n diodes switches, the MEMS devices have better performance in terms of isolation and insertion loss at millimeter-wave frequencies.

There are two classes of RF MEMS phase shifters namely analog and digital. The analog phase shifters provide a continuous variable phase shift from 0 to 360° using varactor capacitive switches [7]; whereas the digital phase shifters provide a discrete or quantized set of phase delays with 1 bit  $180^{\circ}$ , 2 bit  $180^{\circ}/90^{\circ}$  set of delay networks which allow phase shifts of 0, 90, 180 and 270° depending on the combination of bits used [8]. When comparing to the other topologies, the distributed MEMS transmission line (DMTL) phase shifter on silicon wafer proposed in this paper has the advantage of low cost, low loss and small size. In addition, the DMTL phase shifters demonstrated in this work have better performance [9] on simple coplanar waveguide (CPW) transmission lines because CPW based phase shifters are uniplanar. This is one of the main advantages as only one side of the substrate is used; eliminating the need for via-hole process and simplifying the fabrication and integration process with other components. When a single analog control bias voltage is applied to the center conductor, the bridges will be pulled closer to the center conductor, which in turn increases the loading capacitance in the switch, besides varying the

<sup>\*</sup> Corresponding author. Tel.: +65 6790 4336; fax: +65 6792 0415. *E-mail address:* eaqliu@ntu.edu.sg (A.Q. Liu).

<sup>0924-4247/\$ –</sup> see front matter 2004 Published by Elsevier B.V. doi:10.1016/j.sna.2004.10.006

MEMS Bridge (with width of w &length of l)

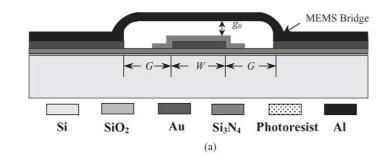

Fig. 1. The configuration for (a) cross sectional view of MEMS shunt switch over CPW transmission line and (b) DMTL.

propagation characteristics and decreasing the phase velocity of the DMTL. The resulting change in the phase velocity of the DMTL produces the TTD phase shifts. This paper analyzes five different designs of DMTL phase shifters based on simple CPW transmission lines and the objective is to optimize the designs with low cost and size, and maximize phase shift per dB loss by varying the impedance size of the transmission lines and the number of switches developed on silicon wafer.

The structure of this paper is organized as follows. Section 2 describes the design of the DMTL phase shifter that covers the designs of single switch and the different types of CPW transmission line. Section 3 provides the fabrication processes of the shunt capacitance switch and the DMTL phase shifters. Section 4 reports the experimental results and discusses the different design of the DMTL phase shifters. Section 5 presents conclusions on the findings.

#### 2. The architecture of the DMTL phase shifter

The DMTL phase shifter consists of a high impedance  $(>50 \Omega)$  CPW transmission line and MEMS shunt switches that are loaded by the periodic placement of variable capacitance. The configuration of the MEMS shunt switch over the CPW transmission line is shown in Fig. 1. *W* is the CPW center conductor width, *G* the CPW gap width,  $g_0$  the bridge height, *s* the periodic spacing of the MEMS bridges on the CPW line, *w* and *l* are the width and length of the MEMS bridge, respectively. The DMTL is connected to 50  $\Omega$  input and output lines to match with probe pads.

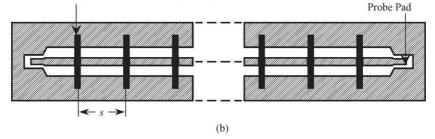

Fig. 2. Equivalent circuit of the loaded DMTL.

### 2.1. Loss versus impedance

An equivalent circuit of the MEMS bridge over the transmission line is shown in Fig. 2, which consists of variable shunt capacitor,  $C_b$  of bridge, the per unit length capacitance,  $C_t$  and the inductance,  $L_t$  of the unloaded CPW transmission line is given by [10].

$$C_{\rm t} = \frac{\sqrt{\varepsilon_{\rm reff}}}{cZ_0} \tag{1a}$$

$$L_{\rm t} = C_{\rm t} Z_0^2 \tag{1b}$$

where  $\varepsilon_{\text{reff}}$  is the effective dielectric constant,  $Z_0$  the characteristics impedance of the unloaded transmission line and *c* is the free space velocity. The characteristic impedance,  $Z_1$  and phase velocity,  $v_1$  of the loaded line are given by

$$Z_{\rm l} = \sqrt{\frac{L_{\rm t}}{C_{\rm t} + C_{\rm b}/s}} \tag{2a}$$

$$v_{\rm l} = \frac{1}{\sqrt{L_{\rm t}(C_{\rm t} + C_{\rm b}/s)}}\tag{2b}$$

The loaded line is designed such that  $Z_1 \approx 50 \Omega$  by choosing an unloaded line impedance of  $Z_0 > 50 \Omega$ .

The Bragg frequency is the frequency at which the characteristic impedance of the line goes to zero, where entire power reflects back. In the case of the DMTL, the up-state inductance–capacitance (LC) resonant frequency of the MEMS bridges is very high (300–600 GHz). As a result, the operation is generally limited by the Bragg frequency  $f_{\text{Bragg}}$  of the loaded line. The Bragg frequency is given by

$$f_{\rm Bragg} = \frac{1}{\pi s \sqrt{L_{\rm t}(C_{\rm t} + C_{\rm b}/s)}} \tag{3}$$

In order to determine the width of the optimal center conductor and the associated unloaded line impedance, both the phase shift and the loss contributed by the loaded line against center conductor width must be determined. The phase shift of the DMTL is determined by the impedance change, which also determines the reflection coefficient of the phase shifter. The phase shift  $\Delta \phi$  of this slow wave structure can be calculated by

$$\Delta \phi = \omega \sqrt{L_t C_t} \left( \sqrt{1 + \frac{C_{\text{lu}}}{sC_t}} - \sqrt{1 + \frac{C_r C_{\text{lu}}}{sC_t}} \right) \tag{4}$$

By substituting the Eqs. (1a), (1b), (2a) and (2b) into (4), the following expression is derived as

$$\Delta \phi = \frac{\omega Z_0 \sqrt{\varepsilon_{\text{reff}}}}{c} \left( \frac{1}{Z_{\text{ld}}} - \frac{1}{Z_{\text{lu}}} \right) \tag{5}$$

where  $Z_{lu}$  and  $Z_{ld}$  are the loaded-line impedance values at the up- and down-state, respectively. The effective capacitance seen by the DMTL at the up-state is  $C_{lu}$ , at the down-state is  $C_{ld}$  and  $C_r$  is capacitance ratio. The impedance varies when the loss of the transmission line is changed due to a change in the amount of capacitance on the transmission line. In order to achieve the maximum amount of phase shift for the minimum amount of insertion loss, the attenuation constant  $\alpha$  for the unloaded CPW transmission line can be expressed as [11]

$$\alpha = \beta \frac{8.86 \times 10^2 R_s \sqrt{\varepsilon_{\text{reff}}}}{4\eta_0 S K(k) K(k')(1-k^2)} \times \left[ \frac{2S}{W} \left\{ \pi + \ln\left(\frac{4\pi W(1-k)}{t(1+k)}\right) \right\} + 2 \left\{ \pi + \ln\left(\frac{4\pi S(1-k)}{t(1+k)}\right) \right\} \right]$$

(6)

$$\alpha_{\rm l} = \alpha \frac{Z_0}{Z_{\rm ld}} \tag{7}$$

$$R_{\rm s} = \sqrt{\frac{\pi f \mu_0}{\sigma}} \tag{8}$$

where  $\alpha_1$  is the loaded line attenuation constant,  $R_s$  the surface resistance, *t* the metal thickness,  $\beta$  the correction of multiplicative factor,  $\eta_0$  the characteristic impedance of free space, *f* the frequency, *W* the width of the CPW center conductor, *G* the width of the CPW gap,  $\sigma$  the conductivity of the metal, *k* the modulus of elliptical integral, *k'* the complementary modulus of *k* for the elliptical integral, *K(k)* and *K(k')* are the complete elliptic integral of the first kind of modulus *k* and

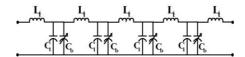

Fig. 3. The line losses and width vs. impedance on Si substrate for  $(W + 2G = 450 \,\mu\text{m})$ .

complete elliptic integral of the first kind of complementary modulus k', respectively.

Another important factor which required careful consideration is the radiation loss. It is present in an unloaded CPW line on a thick dielectric substrate. This is because the wave velocity of the transmission line being greater than the phase velocity of the waves in the dielectric. The loaded line is built on low dielectric constant substrates (quartz or GaAs), the wave velocity of the transmission line is slower than the phase velocity in the dielectric and radiation loss cannot occur. Thus, the line loss per unit length on silicon substrate is higher than that on quartz substrate. The CPW transmission line loss with impedance on silicon substrate is shown in Fig. 3. It is also important to select the input and output port feed lines to match the dimensions and minimize the radiation loss in these lines.

## 2.2. Design of single switch

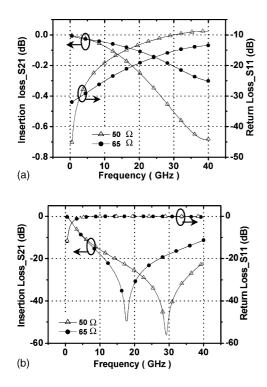

The capacitive MEMS shunt switch is important in the design of the DMTL phase shifter. The capacitive shunt switches [12] are developed on CPW transmission line with different values of characteristic impedances namely, 75, 65 and 50  $\Omega$ . A 675  $\mu$ m high resistivity silicon substrate with 1.5  $\mu$ m thick gold (Au) metal, 1500 Å of Si<sub>3</sub>N<sub>4</sub> dielectric layer is used to insulate the dielectric between the aluminum (Al) material bridge and the CPW transmission line. The aluminum material bridge, which has length of 700 µm, width of 90 µm and thickness of 1.5 µm, is suspended above the CPW transmission line with a  $2 \mu m$  gap. Fig. 4a and b shows the simulated results of the switches at their up- and down-state using the high frequency structure simulator (HFSS) system software [14]. These results show that high impedance loaded CPW transmission line have more superior performance compared to the low impedance loaded line.

It is desirable to have pull-down within the range of  $V_p \le 40$  V, therefore, a wide center conductor and high unloaded impedance is necessary [16]. For a good compromise, it is required to analyze the electrostatically deformed diaphragms. The mechanical design of the capacitance switch involves the application of electrostatic force to deformable structures. The charges are redistributed during the bridge

1

Fig. 4. The simulated results of the switch for both 65 and 50  $\Omega$  (a) up-state and (b) down-state.

structure deformation, which in turn modifies the mechanical load. The pull-down force of the switching bridge due to an applied bias on the center conductor of CPW is given by

$$F = \frac{\varepsilon_0 W w}{2g_0^2} V_{\text{bias}}^2 \tag{9}$$

where  $\varepsilon_0$  is the free-space permittivity and  $V_{\text{bias}}$  is the applied bias voltage as shown in Fig. 1a. The spring constant  $k_s$  of the bridge is approximated by [17]

$$k_{\rm s} = \frac{32Et^3w}{(W+2G)^3} + \frac{8\sigma(1-v)tw}{W+2G}$$

(10)

where *E* is the Young's modulus of the bridge material, *t* the bridge thickness,  $\sigma$  the internal residual stress of the bridge and  $\nu$  is the Poisson's ratio. Then, the pull-down voltage,  $V_{\rm p}$  is given by

$$V_{\rm p} = \sqrt{\frac{8k}{27\varepsilon_0 Ww} g_0^3} \tag{11}$$

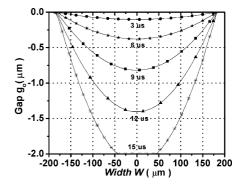

Various factors should be considered in order to analyze the electro-mechanical problems. A model that can accurately predict the dynamic behavior of the MEMS bridge structure should also integrate with several different phenomena. These phenomena include electrostatics, mechanics, residual stress, contact forces, compressible squeeze film damping and impact effects on a microscale. In this paper, a simple one-dimensional nonlinear model is employed to simulate the dynamic behavior of the switch [18]. The differ-

Fig. 5. Changes for the shape of the bridge at different time.

ential motion equation of the bridge can be expressed as

$$mz'' + bz' + K_z z = F_e + F_c$$

(12a)

where *m* is the switch mass, *b* the damping coefficient,  $K_z$  the switch spring constant in the *z*-direction,  $F_e$  the electrostatic force on the switch, and  $F_c$  is the contact force when the switch touches the dielectric. The parameters in Eq. (12a) can be summarized as

$$b = \frac{K_z}{\omega_0 Q} \tag{12b}$$

$$F_{\rm e} = \frac{\varepsilon_0 W w V^2}{2(g_0 - z)^2} \tag{12c}$$

$$Fc = \frac{m1Ww}{(g_0 - z)^3} - \frac{m2Ww}{(g_0 - z)^{10}}$$

(12d)

where  $w_0$  is the resonant frequency and Q is the quality factor.

The pull-down time is calculated based on the assumption that the shape of the deformed bridge remains flat and is independent of its position. Then, the change of the shape of the deformed bridge with the time is simulated and shown in Fig. 5 under a voltage of 40 V. It can be seen from the simulation results, after 15  $\mu$ s, the bridge touches the surface of the dielectric layer. It should be noted that the bridge membrane and the surface of dielectric layer are assumed to be flat. However, simulation results indicate that the switch pull-down time is around tens of microseconds.

## 2.3. Design of CPW transmission line

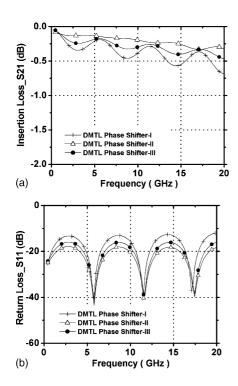

Three types of CPW transmission lines are designed with different impedances on high resistivity silicon wafer. The design parameters of the three types of CPW transmission line are shown in Table 1. In general, these CPW transmission lines differ in terms of their impedances. Phase Shifter-I, Phase Shifter-II and Phase Shifter-III are designed with impedance of 75, 65 and 50  $\Omega$ , respectively, where (*W*+2*G*) are 400, 450 and 300  $\mu$ m, respectively. In each of the design, there are 11 shunt capacitance switches, equally spaced at 800  $\mu$ m and placed above a 10 mm transmission line. It is necessary to have a Bragg frequency of 40 GHz at the maximum capacitive loading [4] and to maintain the loaded line

Table 1

Design parameters of CPW transmission line with experimental results

| Design parameter                | Phase Shifter-I | Phase Shifter-II | Phase Shifter-III |

|---------------------------------|-----------------|------------------|-------------------|

| Impendence, $Z_0(\Omega)$       | 75              | 65               | 50                |

| Width, $W + 2G (\mu m)$         | 400             | 450              | 300               |

| Height, $g_0$ (µm)              | 675             | 675              | 675               |

| Frequency, f <sub>B</sub> (GHz) | 40              | 40               | 40                |

| Number of switch                | 11              | 11               | 11                |

| Space, s (µm)                   | 800             | 800              | 800               |

| Experimental result             |                 |                  |                   |

| S <sub>21</sub> (dB) @ 20GHz    | -3.2            | -2.0             | -3.2              |

| S <sub>11</sub> (dB) @ 20 GHz   | -13             | -17              | -12               |

| Phase @ 20 GHz                  | $100^{\circ}$   | 148°             | 80°               |

impedance within the range of 45–53  $\Omega$  so that the return loss can be below  $-15 \,\text{dB}$  up to Ku band. The simulated results of the various phase shifters which are designed using both HFSS [14] and advanced design system (ADS) [15] system software are shown in Fig. 6. From Fig. 6, the Phase Shifter-II has better and more superior performance than the others in terms of low insertion loss of  $-0.2 \,\text{dB}$  and high return loss of  $-19 \,\text{dB}$ .

# 2.4. Design of DMTL phase shifter

Based on the previous investigation, it is found that Phase Shifter-II exhibits improved performance compared to others and is therefore chosen for further development. There are two improved designs of DMTL. Firstly, the Phase Shifter-IV

Fig. 6. Characterizations of the three-types of DMTL phase shifters in the up-state (a) insertion loss and (b) return loss.

| Table 2                                                           |

|-------------------------------------------------------------------|

| Design parameters of DMTL phase shifter with experimental results |

|                               | -                   | -                   |                    |

|-------------------------------|---------------------|---------------------|--------------------|

| Design parameter              | Phase<br>Shifter-II | Phase<br>Shifter-IV | Phase<br>Shifter-V |

| Impendence, $Z_0(\Omega)$     | 65                  | 65                  | 65                 |

| Width, $W + 2G$ (µm)          | 450                 | 450                 | 450                |

| Height, $g_0$ (µm)            | 675                 | 675                 | 675                |

| Frequency, $f_{\rm B}$ (GHz)  | 40                  | 40                  | 40                 |

| Number of switch              | 11                  | 11                  | 16                 |

| Space, s (µm)                 | 800                 | 500                 | 300                |

| Experimental result           |                     |                     |                    |

| S <sub>21</sub> (dB) @ 20 GHz | -2.0                | -2.0                | -2.3               |

| S <sub>11</sub> (dB) @ 20 GHz | -17                 | -18                 | -15                |

| Phase @ 20 GHz                | 148°                | $180^{\circ}$       | 250°               |

employs 11 shunt capacitance switches which have length of 700  $\mu$ m and width of 90  $\mu$ m. The switches are equally spaced at 500  $\mu$ m on the CPW 65  $\Omega$  and placed above a transmission line with a total length of 7 mm. Secondly, the Phase Shifter-V employs 16 shunt capacitance switches which have length of 700  $\mu$ m and width of 90  $\mu$ m are equally spaced at 300  $\mu$ m on a CPW 65  $\Omega$  above a transmission line with length of 7 mm. The size of these improved designs is smaller than the previous phase shifters where they show an improvement in terms of phase and impedance. A comparison of DMTL phase shifters which are designed with different spacing and number of bridges on high resistivity silicon wafer are shown in Table 2.

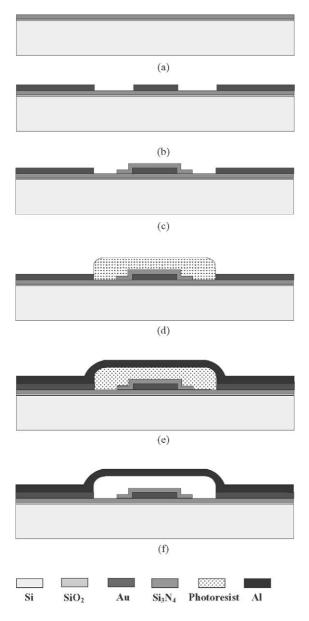

## 3. Fabrication processes

The DMTL phase shifters are fabricated on a 675  $\mu$ mthick of high resistivity silicon substrate ( $\varepsilon_r = 11.9$ ) using the surface micromachining technology. The configurations of the shunt capacitance switch over CPW transmission line and DMTL are shown in Fig. 1.

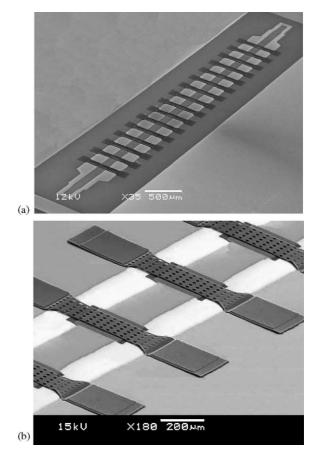

The detailed stages of the fabrication process flow for the DMTL phase shifter with the shunt capacitive switch are shown in Fig. 7. First, Fig. 7a shows the deposition of 300 Å/0.5 µm thermal silicon dioxide and PECVD silicon nitride as buffer layer. Next, Fig. 7b shows the deposition of 1.5 µm thick of gold (Au) which is patterned as CPW. Then, in Fig. 7c, there is a deposition of 1500 Å PECVD silicon nitride and is patterned as a dielectric layer between CPW and bridge. After that, a 2 µm thick of photoresist is coated and patterned as a sacrificial layer and this is shown in Fig. 7d. Later, a 1.5 µm thick of aluminum (Al) film is evaporated and patterned to form the bridge and is shown in Fig. 7e. Finally, Fig. 7f shows the dry release of the bridge and capacitive shunt switch is formed. The performance of the switch depends significantly upon some critical parameters, such as the thickness of the metal membrane, the height of the bridge and the residual stress of the metal. Scanning electron microscope (SEM) micrograph of the fabricated DMTL phase shifter and the enlarged view are illustrated in Fig. 8.

Fig. 7. Details of the fabrication process flow.

# 4. Experimental results and discussions

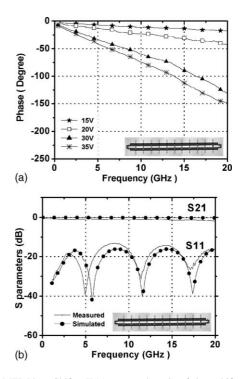

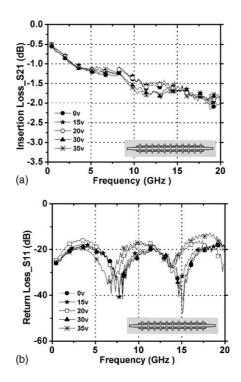

The DMTL measurements and characteristics were made using HP8510C network analyzer and calibrated using the short-open-load-through (SOLT) on-wafer standards. The measurement results of the Phase Shifter-II are shown in Fig. 9a and b compared to the simulation results. The measured insertion loss and return loss with various bias voltages are shown in Fig. 10a and b. These results show that a maximum phase shift of 148° at 20 GHz is achieved with 2 dB insertion loss and less than -15 dB return loss. The up-state capacitance of the shunt switch is calculated as 58 fF, with a series resistance of 0.1  $\Omega$  and a series inductance of 20 pH (which does not have an effect at X-band), which agrees well with the measured results. The measured shunt switch capacitance is 48 fF due to the residual stress in the bridge. Compar-

Fig. 8. SEM micrograph of DMTL phase shifter (a) over view and (b) zoom view.

Fig. 9. DMTL Phase Shifter-II (a) measured results of phase shift at different voltages and (b) measured and simulated results of S-parameters.

ison of the three different types design of CPW transmission line is shown in Fig. 6 where Phase Shifter-II achieves the best experimental results with lower insertion loss, higher return loss and larger phase shift as shown in Table 1.

The phase shift obtained is linear with frequency up to 20 GHz. When the bias voltage is increased, the line impedance reduces from  $52 \Omega$  at 0 V to  $46 \Omega$  at 35 V due to the increase in the capacitive loading of the line as shown in Figs. 2 and 10. The increased loading raises the bridge capacitance from  $C_{tu} = 58$  fF at 0 V to  $C_{td} = 103$  fF at 35 V. In this design, the capacitance ratio,  $C_r$  is 1.8. It can be seen that the shunt switch with high capacitance ratio varactor 1.5–2.5 results in a large loading on the CPW transmission line and therefore a large phase shift. The measured DMTL results are excellent with return loss  $\leq -15$  dB up to Ku band in both the up- and down-state as shown in Figs. 9 and 10, in which the measured result agree well with the simulations results (Fig. 11).

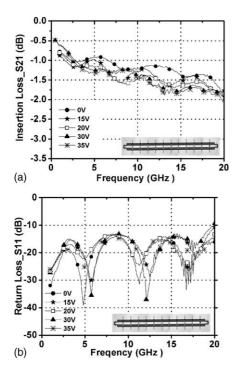

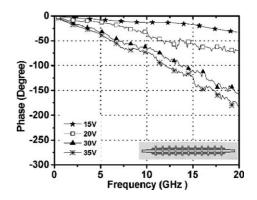

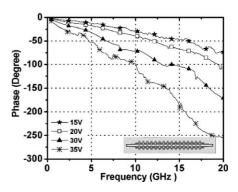

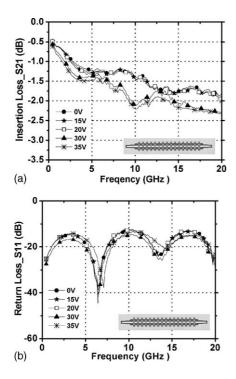

Based on the experimental results of the DMTL Phase Shifter-IV, the insertion loss is below  $-2 \, dB$  along Ku band with the return loss below  $-15 \, dB$  as shown in Fig. 12a and b for different bias voltages. A maximum phase shift of  $180^{\circ}$ at 20 GHz is shown in Fig. 11. Besides, the phase shift is determined by the impedance change of the DMTL, which also determines the reflection coefficient of the phase shifter. Therefore, DMTL Phase Shifter-V was also tested to improve the impedance changes. The DMTL Phase Shifter-V can achieve a maximum phase shift of  $250^{\circ}$  at  $20 \,\text{GHz}$  as shown in Fig. 13, which is higher than DMTL Phase Shifter-IV. The comparisons of the improved designs are shown in

Fig. 10. Measured results of DMTL Phase Shifter-II at different voltages (a) insertion loss and (b) return loss.

Fig. 11. Measured phase shifts of DMTL Phase Shifter-IV at different voltages.

Fig. 12. Measured results of DMTL Phase Shifter-IV at different voltages (a) insertion loss and (b) return loss.

Fig. 13. Measured phase shifts of DMTL Phase Shifter-V at different voltages.

Fig. 14. Measured results of DMTL Phase Shifter-V at different voltages (a) insertion loss and (b) return loss.

Table 2. The measured results of both insertion loss and return loss at different bias voltages are shown in Fig. 14a and b, respectively. From these results, a maximum phase shift of  $250^{\circ}$  at 20 GHz is achieved with 2.3 dB insertion loss and less than -15 dB return loss.

# 5. Conclusion

In this paper, the CPW distributed MEMS transmission line phase shifter based on capacitance shunt switch is designed, simulated and fabricated using the surface micromachining processes. The optimal CPW 65  $\Omega$  DMTL phase shifters which are measured over very wideband can improve phase shift from 148 to 250°. They remain linear in maintaining return loss ( $S_{11} \leq -15 \, \text{dB}$ ) up to Ku band without discontinuity and integration with other components in the transmission line. The Phase Shifter-II has demonstrated to obtain a maximum phase shift of 148° at 20 GHz with 2 dB loss using 11 shunt capacitance switches. The driving voltage reduces the height of the switches, thereby increases the capacitive loading and decreases the phase velocity. The Phase Shifter-V achieves higher phase shift of 250° at 20 GHz with 2.3 dB loss using 16 shunt capacitance switches. The DMTL can be used as a TTD phase shifter by applying a single analog control bias voltage to the center conductor of the CPW transmission line. As a result, the advantages of the DMTL phase shifters in Ku band are lower insertion loss, higher phase shift and easier integration into RF circuit and systems for different military and commercial applications.

#### Acknowledgements

The authors are especially grateful to Associate Professor Law Choi Look and all technicians at Wireless Technology and Position Center and Photonics Research Center for their technical support and help for the RF MEMS device characterization and measurement.

#### References

- [1] C. Goldsmith, J. Randall, S. Eshelman, T.H. Lin, D. Dennistor, S. Chen, B. Norvell, Characteristics of micromachined switches at microwave frequencies, in: IEEE MTT-S International Microwave Symposium Digest, San Francisco, USA, 1996, pp. 1141–1144.

- [2] C. Goldsmith, T.H. Lin, B. Powers, W.R. Wu, B. Norvell, Micromechanical membrane switches for microwave applications, in: IEEE MTT-S International Microwave Symposium Digest, vol. 1, Orlando, FL, USA, 1995, pp. 91–94.

- [3] E.K. Chan, E.C. Kan, R.W. Dutton, P.M. Pinsky, Nonlinear dynamic modeling of micromachined microwave switches, in: IEEE MTT-S International Microwave Symposium Digest, vol. 3, Denver, CO, USA, 1997, pp. 1511–1514.

- [4] E. Brown, RF-MEMS switches for reconfigurable integrated circuits, IEEE Trans. Microwave Theory Tech. 46 (1998) 1868–1880.

- [5] G.E. Ponchak, R.N. Simons, M. Scardelletti, N.C. Varaljay, Microelectromechaincal switches for phase array antennas, in: Salt Lake City, UT, USA, IEEE Antennas and Propagation Society International Symposium Digest, vol. 4, 2000, pp. 2230–2233.

- [6] J.-C. Chiao, MEMS RF devices for antenna applications, in: Asia Pacific Microwave Conference, Sydney, NSW Australia December, 2000, pp. 895–898.

- [7] N.S. Barker, G.M. Rebeiz, Distributed MEMS true-time delay phase shifters and wide-band switches, IEEE Trans. Microwave Theory Tech. 46 (11) (1998) 1881–1890.

- [8] J.S. Hayden, G.M. Rebeiz, 2-Bit MEMS distributed X-band phase shifters, IEEE Microwave Guided Wave Lett. 10 (12) (2000) 540–542.

- [9] J.S. Hayden, A. Malczewski, J. Kleber, C.L. Goldsmith, G.M. Rebeiz, 2 and 4-Bit DC 18 GHz microstrip MEMS distributed phase shifters, in: IEEE MTT-S International Microwave Symposium Digest, Phoenix, USA, 2001, pp. 219–222.

- [10] D.M. Pozar, Microwave Engineering, Addison-Wesley, MA, USA, 1990.

- [11] R.K. Hoffmann, Handbook of Microwave Integrated Circuits, Artech House, Norwood, MA, USA, 1987.

- [12] J.M. Huang, A.Q. Liu, C. Lu, J. Ahn, Mechanical characterization of micromachine capacitive switches design considerations and experimential verification, Sens. Actuators A: Phys. 108 (1–3) (2003) 36–48.

- [14] Ansoft Corporation, Ansoft Maxwell HFSS, Release 8.0.25, http://www.ansoft.com.

- [15] Agilent Technology Inc., ADS 2003A, http://www.agilent.com.

- [16] M.J.W. Rodwell, S.T. Allen, R.Y. Yu, M.G. Case, U. Bhattacharya, M. Reddy, E. Carman, M. Kamegawa, Y. Konishi, J. Pusl, R. Pullela, Active and nonlinear wave propagation devices in ultrafast electronics and optoelectronics, Proc. IEEE 82 (1994) 1037–1059.

- [17] P. Osterberg, H. Yie, X. Cai, J. White, S. Senturia, Self-consistent simulation and modeling of electrostatically deformed diaphragms, in: IEEE Microelectromech, Systematic Conference Proceedings, Oiso, Japan, 1994, pp. 28–32.

- [18] D. Peroulis, S.P. Pacheco, K. Sarabandi, P.B. Linda, Katehi, Electromechanical considerations in developing low-voltage RF MEMS switches, IEEE Trans. Microwave Theory Tech. 50 (1) (2003) 259–270.

# **Biographies**

**W. Palei** received her BE degree in electronic engineering from the Yangon Technological University and the ME degree in electrical and computer engineering from National University of Singapore in 2001. She is currently a Research Associate in the Division of Microelectronic, Nanyang Technological University, Singapore. Her main interest involves passive microwave device modeling, characterization and measurements techniques. Her current interest includes high performance RF MEMS devices for wireless communications and other micro fabrication technologies.

**A.Q. Liu** received his PhD in applied mechanics from National University of Singapore (NUS) in 1994. His MSc was in applied physics and BE was in mechanical engineering from Xi'an Jiaotong University, in 1988 and 1982, respectively. He started to explore MEMS technology in 1995 when he was in the DSO National Laboratory. In 1997, he joined Institute of Materials Research and Engineering (IMRE), National University of Singapore, as a Senior Research Fellow. Currently, he is an Associate Professor at the Division of Microelectronics, School of Electrical and

Electronic Engineering, Nanyang Technological University (NTU). His research interests are MEMS design, simulation and fabrication processes in the field of photonics, lightwave and biophysics.

**A.B. Yu** received BE degree in materials science in 1993 from Shanghai Jiao Tong University and ME degree in electronic material and device in 1996 from Shanghai Jiao Tong University. Currently, he is a Research Associate in Division of Microelectronics, EEE, Nanyang Technological University and PhD candidate toward. His research interests include RF MEMS fabrication, design and simulation.

Arokiaswami Alphones received PhD degree in optically controlled millimeter wave circuits from Kyoto Institute of Technology (Japan) in 1992. Currently, he is an Associate Professor at the School of Electrical and Electronic Engineering, Nanyang Technological University. He is in the editorial review board of IEEE Microwave Theory and Techniques and Microwave and Wireless Components Letters. He has published and presented over 100 technical papers in International Journals/Conferences. His current interests are electro-magnetic analysis on planar RF circuits and integrated optics, EMC testing, microwave photonics, and hybrid fiber-radio systems.