## Wide Dynamic Range CMOS Image Sensor for Star Tracking Applications

### XINYUAN QIAN

School of Electrical and Electronic Engineering

A thesis submitted to the Nanyang Technological University in partial fulfillment of the requirement for the degree of Doctor of Philosophy

### Acknowledgments

I would like express my deepest gratitude to my thesis supervisor, Professor Chen Shoushun, for his insightful technical guidance, steady encouragement and unwavering support throughout my Ph.D. study at NTU. I would also like to extend my appreciation to my thesis co-supervisor, Professor Low Kay Soon, for providing invaluable suggestions and advice in the thesis.

I thank my colleagues in our research group, Dr. Zhao Bo, Dr. Yuan Chao, Mr. Zhang Xiangyu, Mr. Gibran Limi Jaya, for their continuous assistance. They have help made my Ph.D. journal enjoyable, interesting and fruitful. Special thanks to my colleague, Mr. Yu Hang for providing help and suggestions throughout the four years. It won't be easy to complete my research without all of you.

I also thank the School of Electrical and Electronic Engineering of Nanyang Technological University for awarding me the postgraduate scholarship as the financial support in my PhD candidature period.

Lastly, I owe a big debt of gratitude to my parents for their selfless love, inspiring support and continuous encouragement.

## Contents

|   | Ack  | knowle | edgment                        | i    |

|---|------|--------|--------------------------------|------|

|   | List | of Fig | gures                          | vi   |

|   | List | of Ta  | bles                           | xiii |

|   | List | of Al  | obreviations                   | xiv  |

|   | Abs  | stract |                                | xiv  |

| 1 | Intr | oducti | ion                            | 1    |

|   | 1.1  | Thesis | s Motivation                   | 1    |

|   | 1.2  | Thesis | s Objectives                   | 3    |

|   | 1.3  | Thesis | s Contributions                | 4    |

|   | 1.4  | Thesis | s Organization                 | 5    |

| 2 | Bac  | kgroui | nd Study and Literature Review | 7    |

|   | 2.1  | Attitu | de Determination of Satellites | 7    |

|   |      | 2.1.1  | Sun Sensor                     | 8    |

|   |      | 2.1.2  | Magnetometer                   | 8    |

|   |      | 2.1.3  | Gyroscope                      | 9    |

|   |      | 2.1.4  | Earth Horizon Sensor           | 9    |

|   |      | 2.1.5  | Star Tracker                   | 9    |

|   | 2.2  | Review | w of Star Trackers             | 10   |

|   |      | 221    | Overview                       | 10   |

|   |      | 2.2.2  | Star Detection and Star Centroiding                        | 12 |

|---|------|--------|------------------------------------------------------------|----|

|   |      | 2.2.3  | Apparent Magnitude                                         | 14 |

|   |      | 2.2.4  | Star Light Sensitivity                                     | 16 |

|   |      | 2.2.5  | Star Catalog and Star Pattern Recognition                  | 18 |

|   | 2.3  | Funda  | mentals of CMOS Image Sensors                              | 20 |

|   |      | 2.3.1  | Imager Architecture                                        | 20 |

|   |      | 2.3.2  | Photodetection and Photodetectors                          | 22 |

|   |      | 2.3.3  | Basic Pixel Architecture                                   | 24 |

|   |      | 2.3.4  | Passive Pixel Sensor                                       | 24 |

|   |      | 2.3.5  | Performance Analysis                                       | 29 |

|   | 2.4  | Radia  | tion Tolerant CMOS Image Sensor                            | 32 |

|   |      | 2.4.1  | Total Ionizing Dose Effects                                | 33 |

|   |      | 2.4.2  | Single Event Effect                                        | 38 |

|   | 2.5  | Overv  | iew of Wide Dynamic Range CMOS Image Sensors               | 39 |

|   |      | 2.5.1  | Logarithmic Pixel                                          | 39 |

|   |      | 2.5.2  | Well Capacity Adjustment                                   | 43 |

|   |      | 2.5.3  | Dual or Multiple Sampling                                  | 47 |

|   |      | 2.5.4  | Saturation Detection                                       | 50 |

|   |      | 2.5.5  | Comparison of the WDR Techniques                           | 56 |

| 3 | Des  | ign an | d Characterization of Radiation-Tolerant Active Pixel Sen- |    |

|   | sors | O      |                                                            | 57 |

|   | 3.1  |        | luction                                                    | 57 |

|   | 3.2  |        | tion-tolerant Pixel Design                                 | 58 |

|   |      | 3.2.1  | FD Leakage                                                 | 60 |

|   |      | 3.2.2  | Dark Current                                               | 62 |

|   |      |        |                                                            |    |

|   |     | 3.2.3      | Dark Random Noise                                                   | 65  |

|---|-----|------------|---------------------------------------------------------------------|-----|

|   |     | 3.2.4      | Recessed-STI Photodiode                                             | 66  |

|   |     | 3.2.5      | Summary on Pixel Design                                             | 67  |

|   |     | 3.2.6      | Other Design Concerns                                               | 69  |

|   | 3.3 | A Rad      | liation-Tolerant CMOS Image Sensor for VELOX-1 Satellite Mission    | 71  |

|   | 3.4 | Conclu     | usion                                                               | 73  |

| 4 | Nov | el Wio     | de Dynamic Range Architectures for Star Sensors                     | 75  |

|   | 4.1 | Introd     | uction                                                              | 75  |

|   | 4.2 | An Ac      | laptive Integration Time CMOS Image Sensor with Multiple Read-      |     |

|   |     | out Cl     | nannels                                                             | 76  |

|   |     | 4.2.1      | Overview                                                            | 76  |

|   |     | 4.2.2      | Operation Principle                                                 | 77  |

|   |     | 4.2.3      | Sensor Architecture                                                 | 78  |

|   |     | 4.2.4      | Simulation Results                                                  | 85  |

|   |     | 4.2.5      | Implementation and Measurement Results                              | 88  |

|   | 4.3 | A Wid      | le Dynamic Range CTIA Pixel with Dual-Exposure Charge Subtrac-      |     |

|   |     | tion S     | cheme                                                               | 97  |

|   |     | 4.3.1      | Sensitivity Requirement of CMOS Image sensors in Star tracker $\ .$ | 97  |

|   |     | 4.3.2      | Pixel Architecture                                                  | 100 |

|   |     | 4.3.3      | Prototype Chip and Measurement Results                              | 103 |

|   | 4.4 | Conclu     | usion                                                               | 105 |

| 5 | A ( | -<br>Hobal | Shutter Star Centroiding Measurement Sensor                         | 107 |

|   | 5.1 |            | uction                                                              | 107 |

|   | 5.2 |            | Plane SNR Improvement Algorithm                                     | 107 |

|   | 5.3 |            | Architecture                                                        | 108 |

|   | 0.0 | POTIPOI    | 11101110000010                                                      | 100 |

|            | 5.3.1              | Pixel Circuits and Operation     | 110        |

|------------|--------------------|----------------------------------|------------|

|            | 5.3.2              | Pixel Implementation             | 113        |

|            | 5.3.3              | Pixel Noise Analysis             | 114        |

|            | 5.3.4              | Column Signal Path               | 115        |

| 5.         | 4 Meası            | arement Results                  | 116        |

| 5.         | 5 Concl            | usion                            | 121        |

|            |                    |                                  |            |

| 6 C        | onclusio           | on and Future Work               | 124        |

| 6 C        |                    | on and Future Work uding Remarks |            |

|            | l Concl            |                                  | 124        |

| 6.<br>6.   | 1 Concl<br>2 Futur | uding Remarks                    | 124        |

| 6. 6. Auth | 1 Concl<br>2 Futur | uding Remarks                    | 124<br>126 |

# List of Figures

| 2.1  | System block diagram of a typical star tracker                                    | 10 |

|------|-----------------------------------------------------------------------------------|----|

| 2.2  | Focal plane for star centroid calculation                                         | 11 |

| 2.3  | An example ROI with $5\times5$ pixels. The highlighted centroid is calculated     |    |

|      | using the centre of mass algorithm. It can achieve sub pixel accuracy $$ . $$     | 13 |

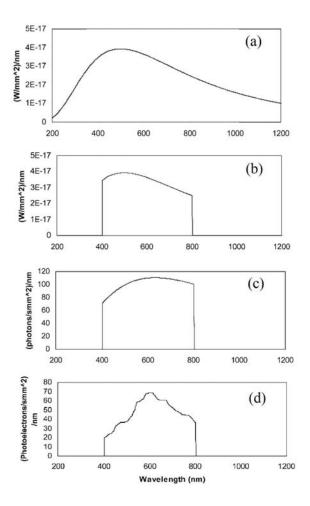

| 2.4  | Apparent magnitude of some celestial objects in the magnitude systems.            | 15 |

| 2.5  | (a) Power spectrum from a $M_v=0$ star on an area of 1mm <sup>2</sup> . (b) Power |    |

|      | influx onto the focal plane. (c) Photon influx onto the focal plane. (d)          |    |

|      | Detectable photons on the focal plane. Adapted from [1]                           | 17 |

| 2.6  | General architecture of a CMOS image sensor                                       | 21 |

| 2.7  | Cross-section view of a N+ diffusion/P-substrate photodiode                       | 22 |

| 2.8  | Schematic and cross-section view of a PPS                                         | 24 |

| 2.9  | Schematic and cross-section view of a 3T APS                                      | 25 |

| 2.10 | Schematic and cross-section view of a 4T APS                                      | 27 |

| 2.11 | A simplified CMOS image sensor model, adapted from $[2]$                          | 31 |

| 2.12 | Band diagram of a MOS capacitor with positive gate bias. The process of           |    |

|      | radiation-induced device degradation is illustrated, adapted from $[3]$           | 34 |

| 2.13 | Cross-section of a transistor where positive charges due to ionizing radia-       |    |

|      | tion are accumulated at the edges of the transistor                               | 35 |

| 2.14 | (a) Normal transistor layout, (b) Enclosed layout transistor                      | 36 |

| 2.15 | Cross section of a recessed-STI photodiode                                        | 38 |

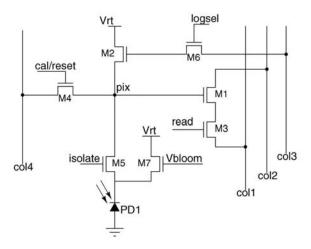

| 2.16 | Conventional 3T logarithmic APS                                               | 40 |

|------|-------------------------------------------------------------------------------|----|

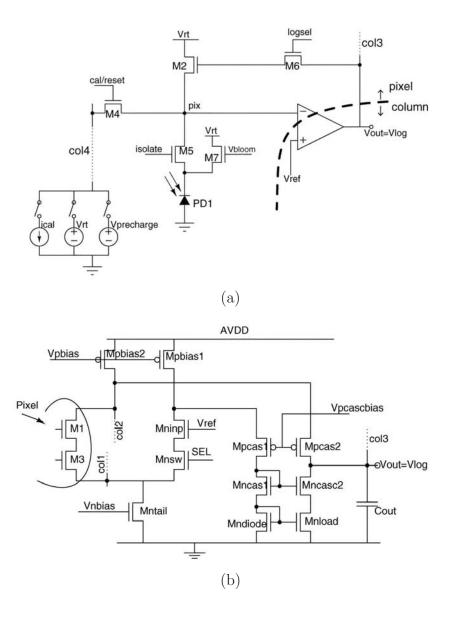

| 2.17 | Schematic of the linear-logarithmic pixel, adapted from [4]                   | 41 |

| 2.18 | (a) Logarithmic pixel configuration and (b) Column amplifier for logarith-    |    |

|      | mic operation, adapted from [4]                                               | 42 |

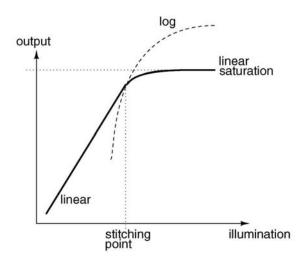

| 2.19 | Combined linear-logarithmic response curve, adapted from [4]                  | 43 |

| 2.20 | Pixel schematic, adapted from [5]                                             | 44 |

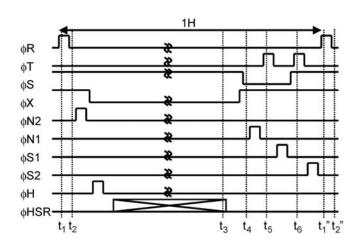

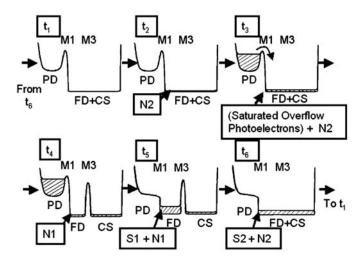

| 2.21 | Timing diagram of the pixel operation, adapted from [5]                       | 45 |

| 2.22 | Potential diagram of the pixel operation, adapted from [5]                    | 45 |

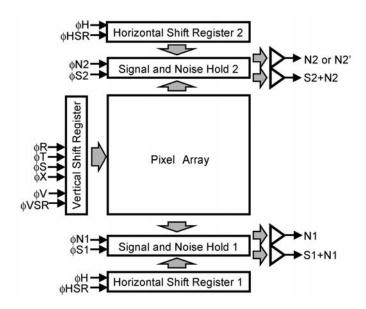

| 2.23 | Block diagram of the sensor architecture, adapted from [5]                    | 46 |

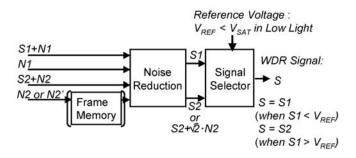

| 2.24 | Signal processing flowchart of the dynamic range extension, adapted from [5]. | 46 |

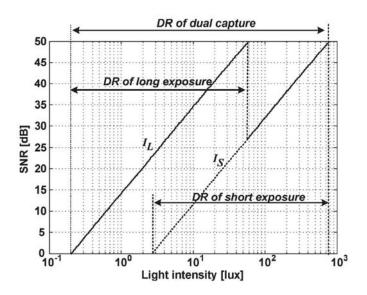

| 2.25 | SNR versus light intensity, adapted from [6]                                  | 49 |

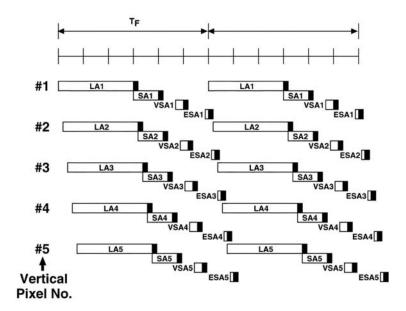

| 2.26 | Timing diagram of the multiple sampling with different exposure lengths,      |    |

|      | adapted from [7]. Four exposure lengths are used, namely LA: long accu-       |    |

|      | mulation, SA: short accumulation, VSA: very short accumulation, ESA:          |    |

|      | extremely short accumulation                                                  | 50 |

| 2.27 | (a)PWM and (b) PFM encoding scheme of exposure information, adapted           |    |

|      | from [8]                                                                      | 51 |

| 2.28 | SNR comparison between a conventional APS and a time-domain pixel as          |    |

|      | a function of illumination levels, adapted from [8]                           | 52 |

| 2.29 | HDR pixel concept, adapted from [9]                                           | 53 |

| 2.30 | HDR pixel operation timing, adapted from [9]                                  | 54 |

| 2.31 | Schematic diagram of the HDR pixel circuit, adapted from [9]                  | 55 |

| 2.32 | Layout of the pixel, adapted from [9]                                         | 55 |

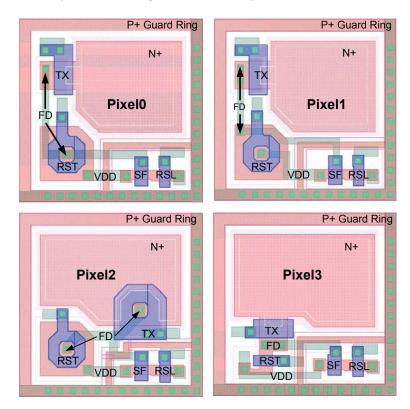

| 3.1  | Layout of the four different pixel types                                      | 59 |

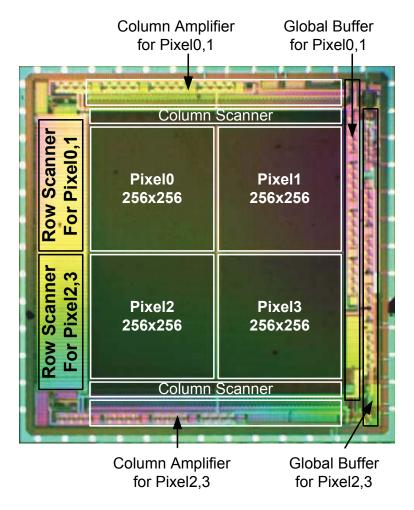

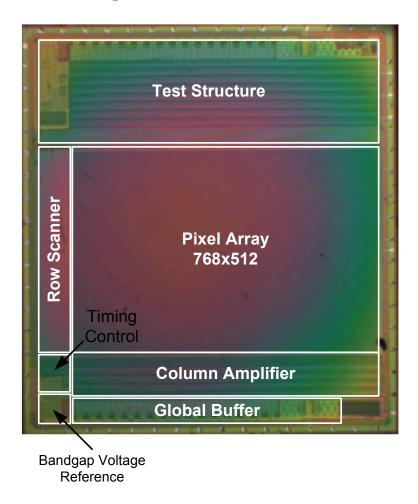

| 3.2  | The microphotograph of the prototype chip. There are four pixel sub-array     | 30 |

|      | on the chip. Main building blocks are highlighted                             | 61 |

|      | 1                                                                             |    |

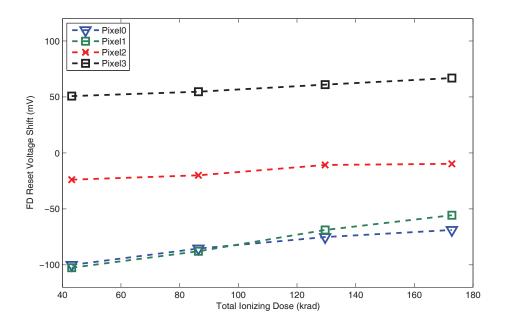

| 3.3  | FD reset voltage increase as a function of total ionizing radiation dose for |    |

|------|------------------------------------------------------------------------------|----|

|      | four implemented pixel types                                                 | 62 |

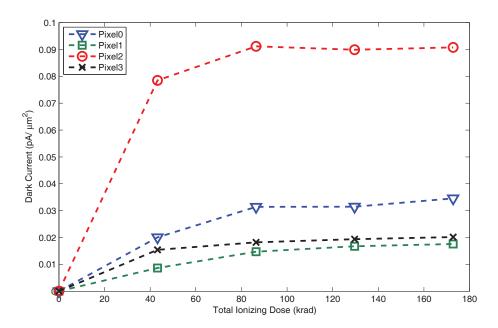

| 3.4  | Average dark current with regard to total ionizing radiation dose for four   |    |

|      | implemented pixel configurations                                             | 63 |

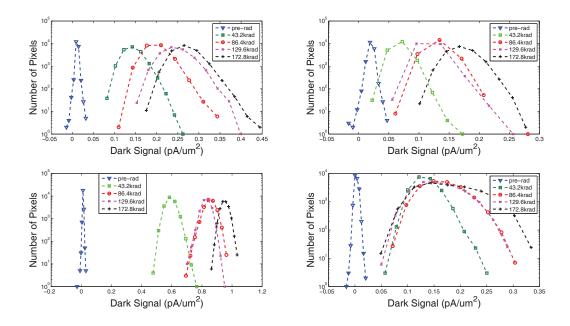

| 3.5  | Histogram of dark current                                                    | 64 |

| 3.6  | Dark random noise (standard deviation value) before and after ionizing       |    |

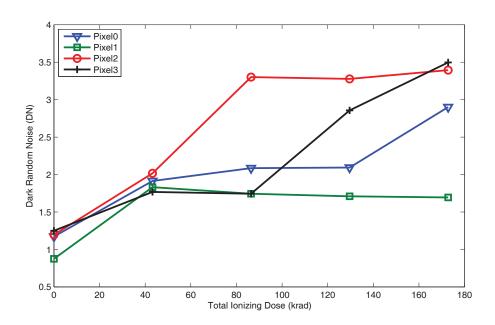

|      | radiation for all the pixel types                                            | 65 |

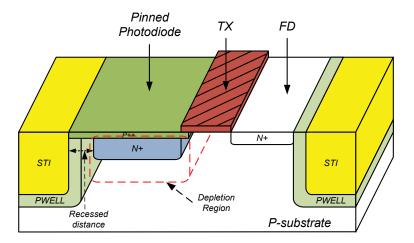

| 3.7  | Pinned photodiode cross-section details                                      | 66 |

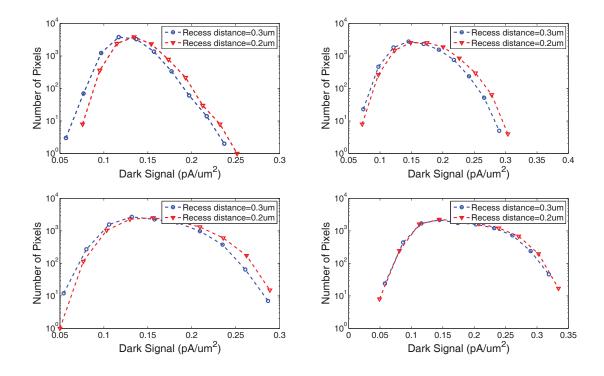

| 3.8  | Histogram of dark signal regarding recessed distance                         | 67 |

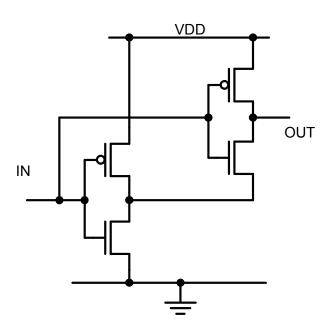

| 3.9  | Radiation tolerant inverter structure used in D flip-flop                    | 69 |

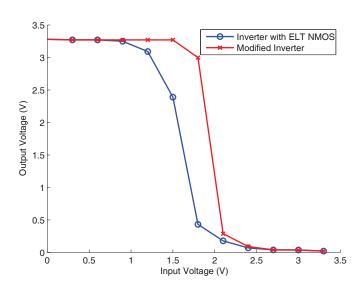

| 3.10 | Comparison of inverter voltage transfer curve between standard structure     |    |

|      | with ELT NMOS and the radiation-tolerant modified structure                  | 70 |

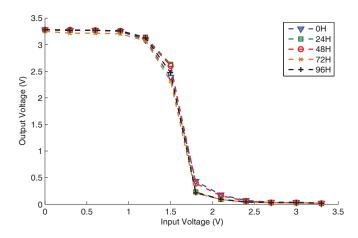

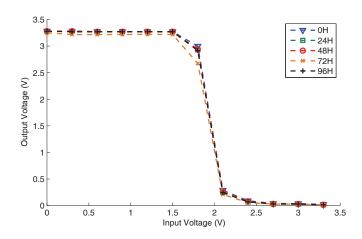

| 3.11 | Voltage transfer curve of the standard inverter with ELT NMOS under          |    |

|      | different ionizing radiation dose                                            | 71 |

| 3.12 | Voltage transfer curve of the radiation-tolerant modified inverter under     |    |

|      | different ionizing radiation dose                                            | 71 |

| 3.13 | Chip microphotograph of the radiation-tolerant CMOS image sensor             | 72 |

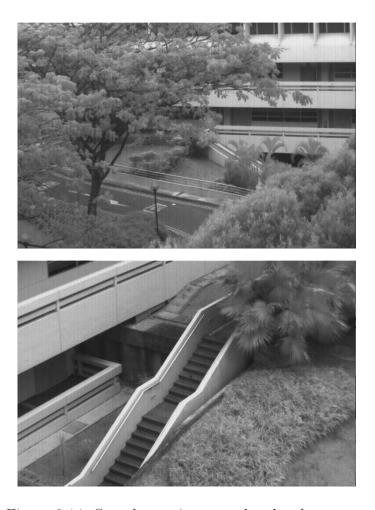

| 3.14 | Sample raw images taken by the sensor                                        | 73 |

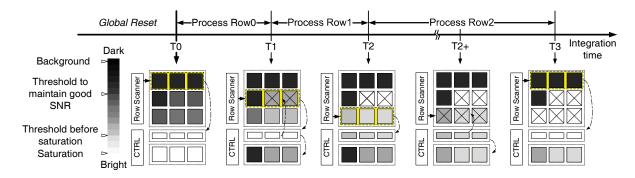

| 4.1  | Operation principle of the adaptive-integration-time readout scheme          | 77 |

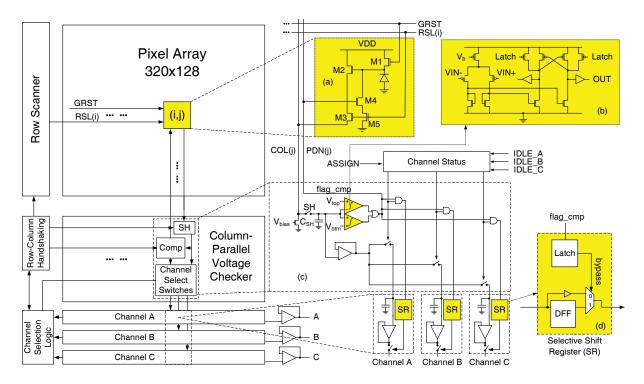

| 4.2  | Sensor architecture. Main building blocks include a pixel array, column-     |    |

|      | parallel comparison circuits, three readout channels, row scanner and chan-  |    |

|      | nel assignment controller                                                    | 78 |

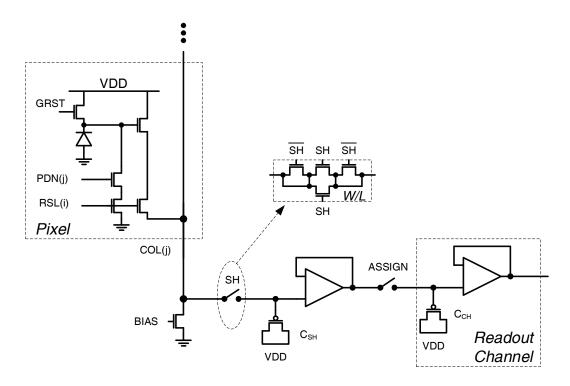

| 4.3  | Analog signal path from the pixel to a readout channel                       | 80 |

| 4.4  | Timing diagram of the sensor operation                                       | 81 |

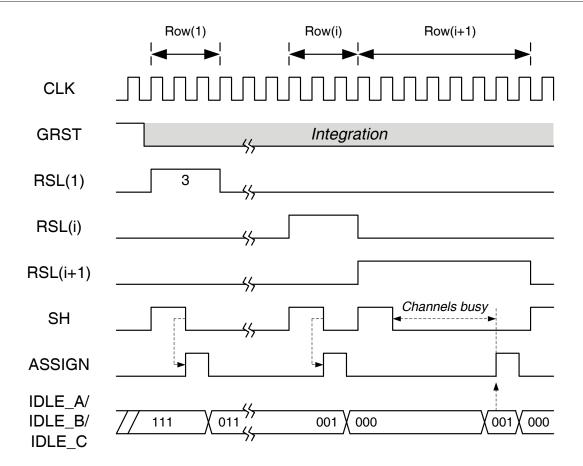

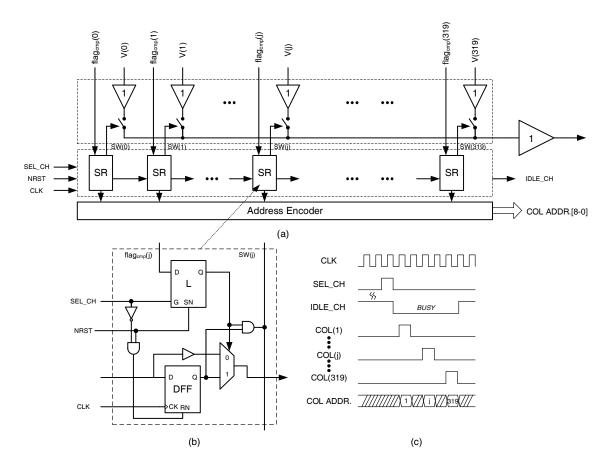

| 4.5  | The architecture of the readout channel                                      | 82 |

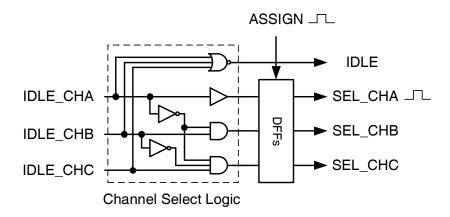

| 4 6  | Channel select and assignment logic                                          | 83 |

| 4.7  | Illustration of different pixels' responses. Pixels with different illumination                |    |

|------|------------------------------------------------------------------------------------------------|----|

|      | level will have its own integration time                                                       | 84 |

| 4.8  | Simulation results for a $320 \times 128$ Lena image under sensor operation.                   |    |

|      | In(a)-(d), top threshold is set to 3500 and bottom threshold are 1500,                         |    |

|      | 2500, 3000 and 3300, respectively. In(e)-(h), top threshold is set to 3000                     |    |

|      | and bottom threshold are 1000, 2000, 2500, 2800, respectively. $In(i)$ -(l),                   |    |

|      | top threshold is set to 2500 and bottom threshold are 500, 1000, 2000 and                      |    |

|      | 2300, respectively                                                                             | 86 |

| 4.9  | Simulation results for a $320 \times 128$ star field image under sensor operation.             |    |

|      | In(a)-(d), top threshold is set to 3500 and bottom threshold are 1500,                         |    |

|      | 2500, 3000 and 3300, respectively. $In(e)$ -(h), top threshold is set to 3000                  |    |

|      | and bottom threshold are 1000, 2000, 2500, 2800, respectively. $In(i)$ -(l),                   |    |

|      | top threshold is set to 2500 and bottom threshold are 500, 1000, 2000 and                      |    |

|      | 2300, respectively                                                                             | 86 |

| 4.10 | Readout percentage of the (a) Lena and (b) star image                                          | 88 |

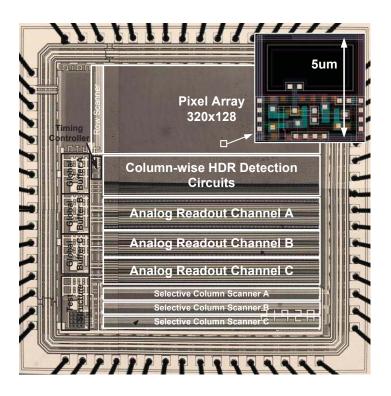

| 4.11 | Chip microphotograph                                                                           | 89 |

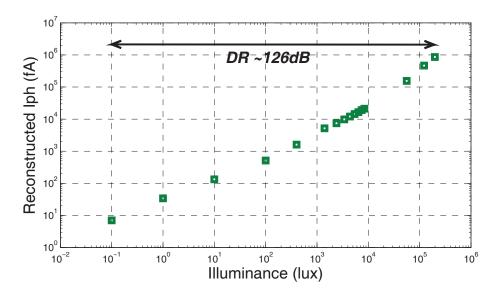

| 4.12 | Measured photocurrent with regard to incident illuminance                                      | 90 |

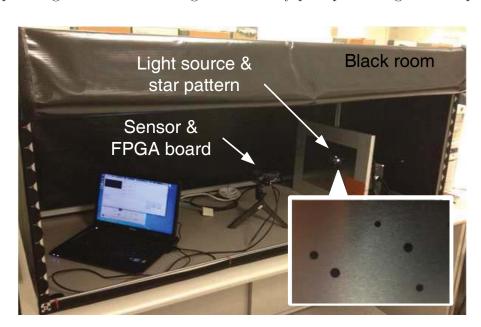

| 4.13 | Measurement setup for capturing "star" images                                                  | 91 |

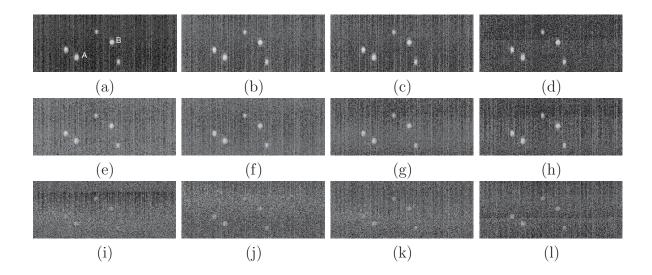

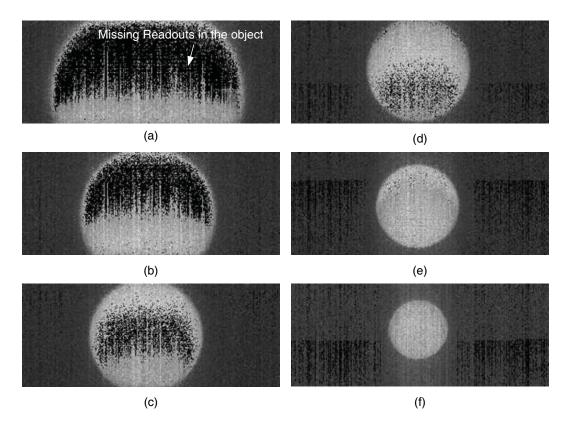

| 4.14 | Raw sample images for simulated star-pattern measurement under differ-                         |    |

|      | ent parameter settings. Images in the first row (a)-(d), top threshold is                      |    |

|      | set to 500 mV and bottom threshold are 250 mV, 300 mV, 350 mV and                              |    |

|      | $450~\mathrm{mV},$ respectively. In (e)-(h), top threshold is changed to $600~\mathrm{mV}$ and |    |

|      | In (i)-(l), top threshold is set to 700 mV. Two "stars", marked as A and                       |    |

|      | B, are selected for centroiding evaluation                                                     | 92 |

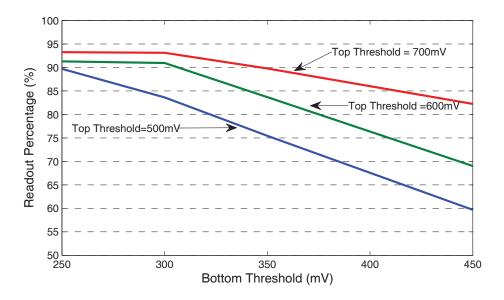

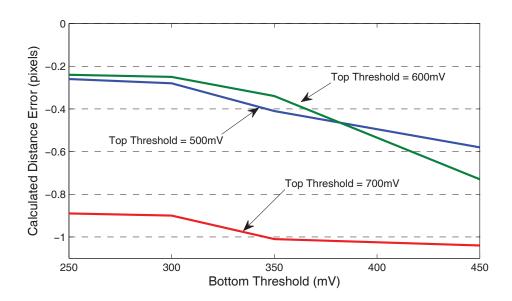

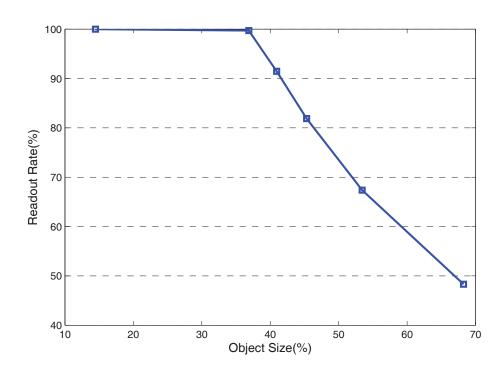

| 4.15 | Readout percentage of the simulated star-pattern images                                        | 93 |

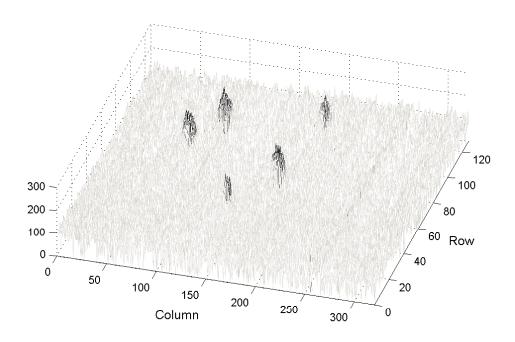

| 4.16 | Gray-scale mapping of the star image in Fig. 4.14(a)                                           | 94 |

| 4.17 | Calculated distance error with different top threshold voltage                | 95  |

|------|-------------------------------------------------------------------------------|-----|

| 4.18 | Example images of uniform circular objects with different size                | 96  |

| 4.19 | Readout percentage for the pixels inside the objects                          | 97  |

| 4.20 | Stars travel on the focal plane during integration due to the satellite's     |     |

|      | orbit. The travel distance $L$ is expressed in pixels in one dimension, where |     |

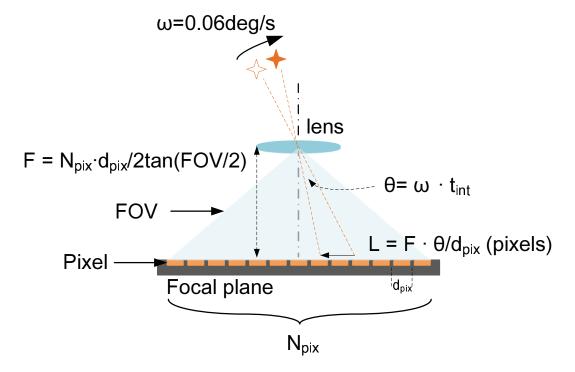

|      | $d_{pixel}$ is the pixel pitch                                                | 98  |

| 4.21 | (a) and (b) are simulated static star images and integration results, re-     |     |

|      | spectively. (c) and (d) are simulated dynamic star images and integration     |     |

|      | results with star shift, respectively. They are captured with the same inte-  |     |

|      | gration time. When the star center moves to its neighboring pixel during      |     |

|      | integration, the star energy is then spread over more pixels. The resulting   |     |

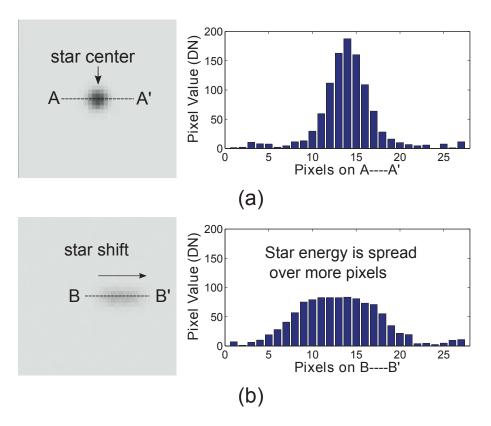

|      | "tail effect" does not increase the signal magnitude                          | 99  |

| 4.22 | Global-shutter timing difference between (a) conventional and (b) pro-        |     |

|      | posed dual exposure high dynamic range method. In conventional method,        |     |

|      | there is a frame readout between two exposures. The readout time can be       |     |

|      | several milliseconds long. For example, 100 ms is expected if we assume       |     |

|      | an array of 2M pixels with 20MHz clock frequency. It causes a shift of $0.3$  |     |

|      | pixels on focal plane between two exposures, which adds to the centroiding    |     |

|      | error                                                                         | 100 |

| 4.23 | Pixel functional block diagram                                                | 101 |

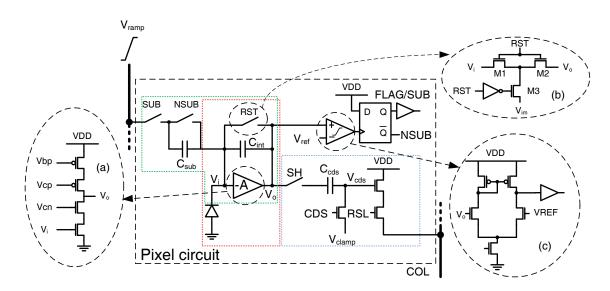

| 4.24 | The schematic of the pixel circuit. (a) the schematic of the OTA, (b) the     |     |

|      | reset switch and (c) the comparator are shown respectively                    | 101 |

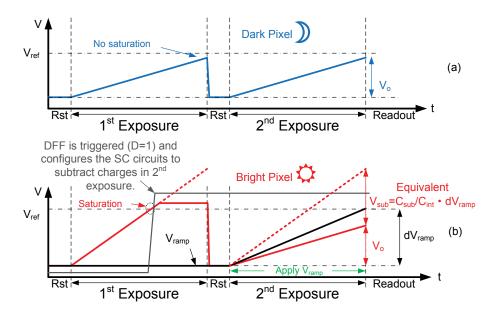

| 4.25 | Pixel operation timing diagram                                                | 102 |

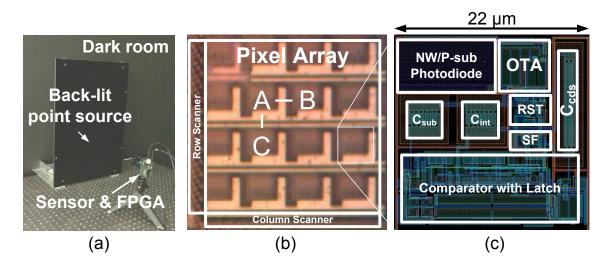

| 4.26 | (a) Test setup, (b) chip microphotograph and (c) pixel layout                 | 104 |

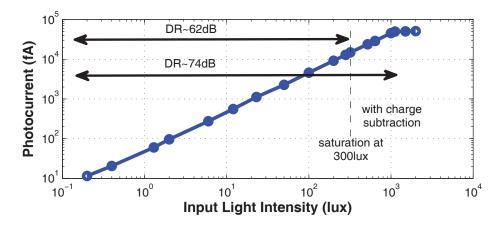

| 4.27 | Measured photocurrent with regard to incident light intensity. The pixel      |     |

|      | saturates at around 300 lux. With charge subtraction, the dynamic range       |     |

|      | increases by approximately 12dB and saturates at around 1100 lux              | 104 |

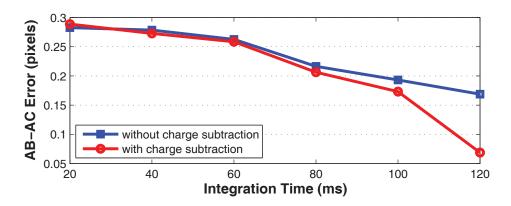

| 4.28 | Measured $AB-AC$ distance error at different integration times. "star"                  |     |

|------|-----------------------------------------------------------------------------------------|-----|

|      | pixels does not saturate when integration time is small, so charge subtrac-             |     |

|      | tion does not improve the error obviously. However, saturation occurs in                |     |

|      | "stars" after about 80 ms. With charge subtraction, centroiding accuracy                |     |

|      | improves much better compared with the saturated one                                    | 105 |

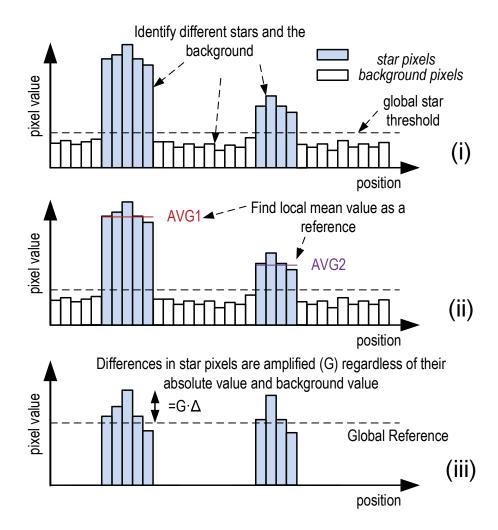

| 5.1  | Star thresholding and local average calculation. The global star threshold              |     |

|      | is used to locate star region, and the mean value is calculated within the              |     |

|      | region. In this way, each different star will have an individual mean value.            |     |

|      | This mean value is then used as a local reference for signal amplification.             | 109 |

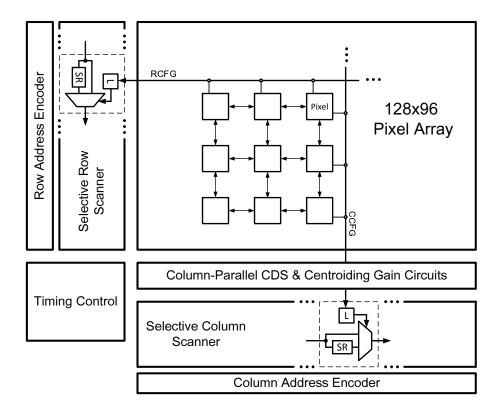

| 5.2  | Block diagram of the proposed sensor architecture                                       | 110 |

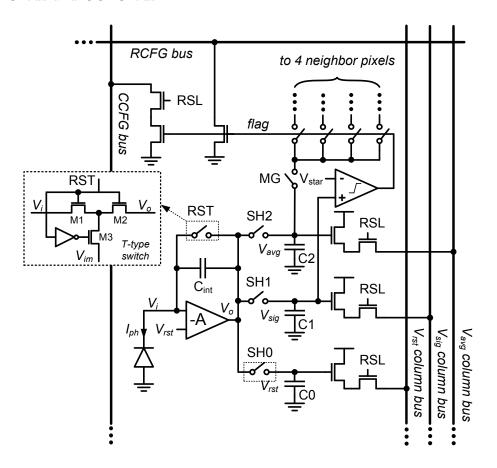

| 5.3  | Schematic of the pixel circuits. A T-type switch is used for $RST$ switch.              | 111 |

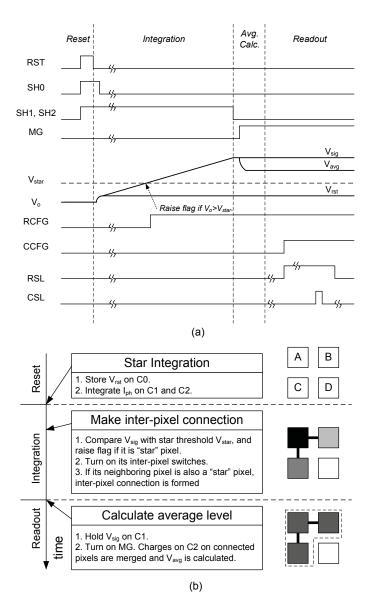

| 5.4  | (a) Timing diagram and (b) operation flow of the pixel circuits. An ex-                 |     |

|      | ample block diagram of 2 $\times$ 2 pixel array demonstrates the inter-pixel            |     |

|      | operation. Before integration, pixel reset values are sampled on the C0                 |     |

|      | capacitor in order to perform. During integration, pixels that reaches star             |     |

|      | threshold make connection with its neighboring pixels. pixels can make                  |     |

|      | such connections until the end of integration. At the end of the integration,           |     |

|      | the connected pixels formes a star cluster (pixel A, B and C). When the                 |     |

|      | ${\cal M}{\cal G}$ is turned on, charges on C2 of these pixels are merged and averaged. |     |

|      | The local reference $V_{avg}$ is accordingly calculated                                 | 112 |

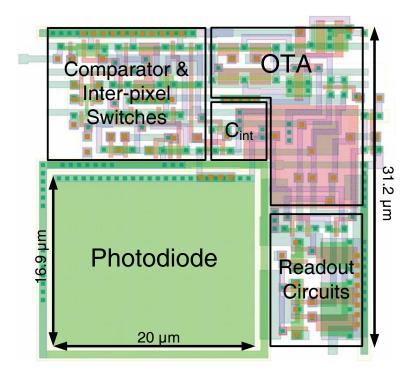

| 5.5  | Pixel layout                                                                            | 113 |

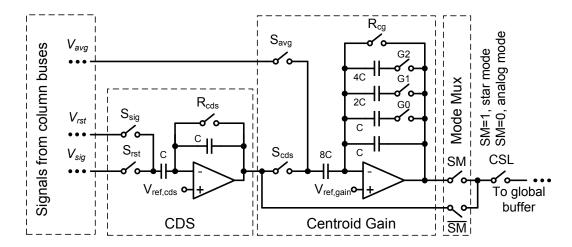

| 5.6  | Column signal path which is composed two-stage switched-capacitor circuits              | 115 |

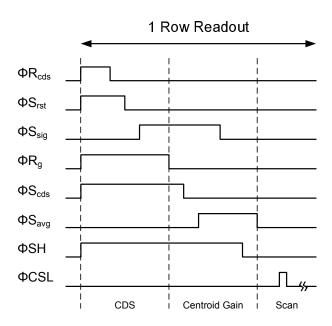

| 5.7  | Timing diagram of column signal path for readout of one row                             | 116 |

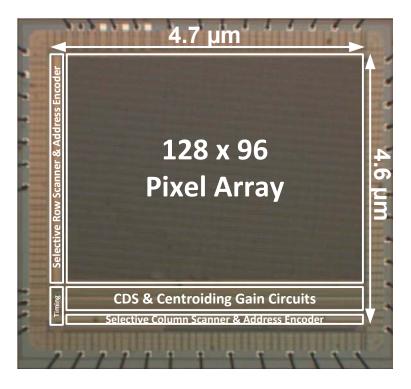

| 5.8  | Chip microphotograph                                                                    | 117 |

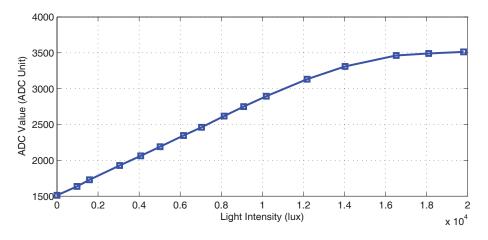

| 5.9  | Pixel response curve                                                                    | 117 |

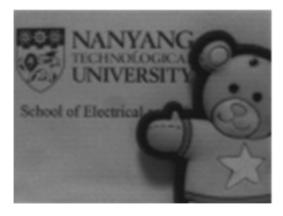

| 5.10 | Sample images in snapshot mode                                                          | 118 |

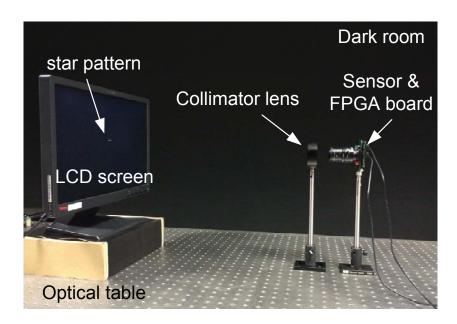

| 5.11 | Centroid measurement setup                                                  | 119 |

|------|-----------------------------------------------------------------------------|-----|

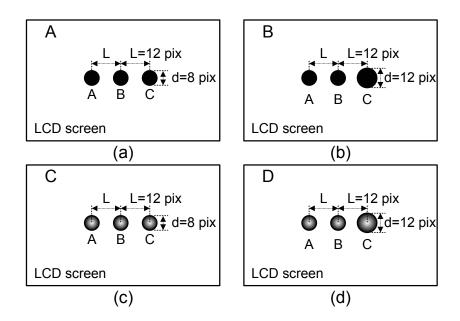

| 5.12 | Test pattern: three circular spots at equal distance on a LCD screen. (a)   |     |

|      | Pattern A: uniform profile and uniform size. (b) Pattern B: uniform profile |     |

|      | and different size. (c) Pattern C: gaussian profile and uniform size. (d)   |     |

|      | Pattern D: gaussian profile and different size                              | 120 |

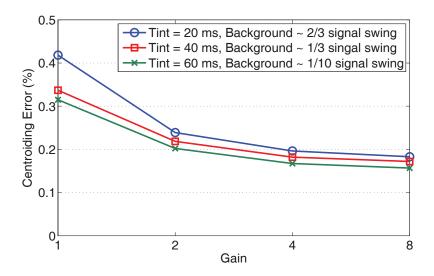

| 5.13 | Measured relative distance error.                                           | 121 |

## List of Tables

| 2.1 | Star Radiation and Luminance                                                          | 19  |

|-----|---------------------------------------------------------------------------------------|-----|

| 2.2 | Comparison of the WDR Techniques                                                      | 56  |

| 3.1 | Summary of the Pixel Constitutions for Four Pixel Types (Sized in $\mu \mathrm{m})$ . | 60  |

| 3.2 | Characterization Summary of Each Pixel Type                                           | 60  |

| 3.3 | Main Feature Comparison of Both Image Sensors                                         | 74  |

| 4.1 | Performance Summary of the Sensor                                                     | 90  |

| 4.2 | Performance Summary and Comparison                                                    | 105 |

| 5.1 | Performance Summary of the Sensor                                                     | 118 |

| 5.2 | Centroiding accuracy comparison with Aptina MT9M032                                   | 123 |

| 5.3 | Centroiding Accuracy Improvement with FPN cancellation                                | 123 |

### List of Abbreviations

ADC Analog-to-Digital Converter ADCS Attitude Determination and Control System APS Active Pixel Sensor CCDCharge Coupled Device CDS Correlated Double Sampling CMOS Image Sensor CIS CMOS Complementary Metal-Oxide-Semiconductor CTIA Capacitive Transimpedance Amplifier DAC Digital-to-Analog Converter DFF D-Flip-Flop ELT **Enclosed Layout Transistor**

FD Floating Diffusion FF Fill Factor

FPN Fixed Pattern Noise

FOV Field of View FOX Field Oxide

HDR High Dynamic RangeLEO Low-Earth Orbit

OTA Operational Transconductance Amplifier

PFM Pulse Frequency Modulation PWM Pulse Width Modulation

PD Photodiode

PPD Pinned Photodiode

QE Quantum Efficiency

SEE Single Event Effect

SOC System on Chip

SNR Signal to Noise Ratio

STI Shallow Trench Isolation

TID Total Ionizing Dose

### Abstract

Recent trends in space technologies highlight the importance of star trackers. Star trackers are optical-electronic devices that measure starlight directions. They are the most accurate sensors for 3-axis satellite attitude estimation. Current generation star trackers generally use CMOS image sensors as their star sensor thanks to this type of sensors inherent advantages of low power, low cost and, more importantly, their ability to integrate system-on-a-chip technology. This high degree of integration reduces process complexity and improves efficiency in attitude data processing. It also allows smaller, lighter star tracker designs, a distinct advantage in miniaturized space platforms. Conventional CMOS image sensors, however, do not meet design specifications for use in a star tracker, where several important limitations and design challenges have to be overcome. Most offthe-shelf CMOS image sensors are not space qualified to withstand the space radiation environment. Not only can radiation effects significantly exacerbate a sensors performance degradation, but they can also permanently damage the sensor itself. Radiation tolerance is therefore a critical prerequisite for such charge-sensitive devices destined for use in space applications. A wider dynamic range is also required if a wide range of star brightness is to be detected accurately, while active pixel sensors in deep submicron CMOS technologies fall short of meeting aggressive high dynamic range requirements due to their supply voltage limitations. Moreover, high-sensitivity pixels and low-noise readout circuits capable of achieving a high signal-to-noise ratio are essential for high centroiding accuracy. This thesis focuses primarily on the above-mentioned design aspects of CMOS image sensors. Its main contributions can be separated into three parts.

Firstly, radiation-induced impact on active pixel sensors were investigated. Different radiation hardening techniques were validated using silicon implementations to outline proper design guidelines for CMOS image sensors to be used in space applications. Secondly, two novel wide dynamic range CMOS image sensor architectures were proposed. One of them allows adaptive integration time for each pixel and expedites the readout using multiple readout channels. The other applies a dual-exposure charge subtraction strategy to extend dynamic range, and, accordingly, a new high-sensitivity capacitive transimpedance amplifier pixel was proposed. Finally, with very large scale integration (VLSI) architectures to improve centroiding accuracy in mind, a global-shutter CMOS image sensor with star-region SNR improvement was proposed.

## Chapter 1

### Introduction

### 1.1 Thesis Motivation

Attitude knowledge is important for modern space platforms. It must be measured and controlled for a variety of operations, such as pointing solar panels at the sun, aligning high-gain communications links with ground stations or attitude acquisition for scientific payloads. Missions like these, requiring high attitude precision, naturally imply a need for high-accuracy attitude sensors. Attitude sensors are widely used to detect an aircrafts orientation with respect to a reference frame in space. They are classified into different categories for example gyroscopes, sun sensors, magnetometers or star trackers - according to the reference vectors they use. One of these sensor types, the star tracker, measures starlight directions using solid-state imaging devices. Since starlight directions are fixed in the inertial reference frame (ECI frame), they are known to be extremely accurate. Star trackers are therefore considered the most accurate kind of sensor, capable of offering bore sight accuracies in terms of arcseconds. Modern space platforms are usually equipped with a star tracker to satisfy their need for high-accuracy attitude measurement.

CMOS image sensor technologies have evolved so rapidly over the last few decades that these devices have now outpaced Charge-Couple Devices (CCDs) and are widely used in a wide range of space applications, including robotic and navigation vision systems, astronomical and earth imaging, land and rover cameras, x-ray detectors and star trackers. Recently emerging trends in miniaturized satellite missions, such as microsatellites and pico-satellites, have favored the deployment of CMOS-based star trackers. A micro-satellite has a wet mass of several tens of kilograms. To reduce the amount of hardware or firmware, and thus to reduce mass and weight, the circuit integration capability of System-on-Chip (SoC) design is vital. Size scaling also limits the number of on-board solar cells, and the sensors used need to consume little power due to the strict power budget. The main advantages of CMOS image sensors are their low power consumption at low voltage operation, their high integration capability for SoC design, their potential for radiation resilience, and the cost effective solutions they provide from a standardized fabrication process. These positive features are particularly beneficial for star trackers in miniaturized satellite missions.

Most commercial off-the-shelf CMOS image sensors are lacking in any specific design consideration of relevance to star trackers. Conventional Active Pixel Sensors (APS) are not qualified for direct usage in space missions. Low-Earth-Orbit (LEO) satellites are exposed to a harsh radiation environment, with grammar rays and high energy particles. Radiation hardness is critical for electronics deployed in space applications, especially the charge-sensitive devices found in CMOS image sensors, which need to be able to survive the radiation environment during long-term space missions. Performance degradation caused by total ionizing dose (TID) can also be a significant source of measurement noise, which increases measurement error. APS do not have sufficient dynamic range to accommodate a wide span of star brightness with a high signal-to-noise ratio (SNR). Wide dynamic range increases the number of detectable stars in the Field of View (FOV). Since the average number of stars in the FOV is also essential for accuracy, wide dynamic range also plays an important role in increasing overall tracking accuracy. Another critical issue

in APS is sensitivity to starlight. It is very difficult for APS to detect a limited number of photons from stars, especially when exposure time is also limited. Since photoelectrons are directly integrated on the large photodiode capacitance, voltage change is small. The SNR obtained is therefore low, making APS unsuitable for high-accuracy star trackers.

The above-described issues set new design specifications for next generation high-accuracy CMOS-based star trackers. Radiation tolerant pixel devices, in particular for CMOS image sensor technologies, are essential in this application. Neither is it easy to achieve high dynamic range and high sensitivity at the same time. This imposes difficult design trade-offs and makes it necessary to seek the specific optimization of each design parameter. My research in this thesis has been motivated precisely by these considerations. To summarize, this thesis investigates various design aspects of a CMOS image sensor for star trackers, exploring VLSI solutions at different levels, from system innovation and circuit techniques to device optimization. It is expected that the findings of this thesis will help improve the measurement performance of the star trackers used in NTUs current attitude determination and control system (ADCS) and prove useful in NTUs future satellite missions.

### 1.2 Thesis Objectives

The overall objective of this thesis is to develop wide dynamic range CMOS image sensors for star tracking. Three major areas are covered:

- (i) To investigate radiation effects on CMOS image sensors used in the space radiation environment and design radiation-tolerant pixels.

- (ii) To design new pixel circuit and sensor architecture featuring improved dynamic range suitable for use in star trackers.

(iii) To explore smart sensor architecture capable of aiding star centroiding measurement and improving centroiding accuracy.

#### 1.3 Thesis Contributions

The contributions of this thesis are summarized in the following items:

- (i) Radiation-induced impacts on CMOS image sensors were investigated. In particular, total ionizing radiation effects on 4T APS were analyzed. Characterizations from fabricated chips mainly showed dark current increase and temporal noise increase due to the ionizing radiation on the pixel devices. The characterization also showed that the main radiation-induced degradation mechanism in a 4T APS was due to complex photosensitive regions. To mitigate these radiation influences, various radiation hardening techniques using layout enhancement were employed on four proposed pixels. The techniques were then compared to verify their usefulness and effectiveness. The comparison results provided a guideline for radiation-tolerant pixel design as an economic countermeasure to the total ionizing dose effects.

- (ii) Two novel wide dynamic range CMOS image sensor architectures were proposed. The first approach was based on the time-domain operation principle of adaptive integration time. Rather than conventional time-domain pixels, which are large and complex, the proposed architecture only utilized pixels with a compact footprint. This was achieved by cyclically checking the integration voltage of a row of pixels in column-parallel circuits, throughout exposure. Brighter pixels could thus be "marked" and read out first. Dark pixels continued to integrate until their voltages fell into a voltage window. Pixel voltage and its sampling time were used together to reconstruct the image. The second approach extended the dynamic range by

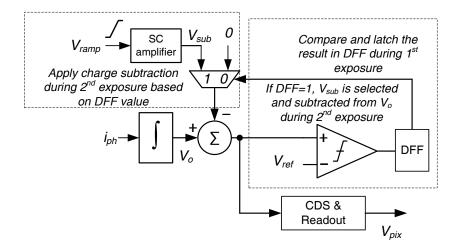

means of a dual-exposure charge subtraction strategy. A capacitive transimpedance amplifier (CTIA) was used to achieve high sensitivity at the same time.

(iii) A novel smart CMOS image sensor capable of assisting in star centroiding was proposed. An adaptive SNR improvement algorithm was integrated on the focal plane to improve centroiding accuracy. A corresponding sensor architecture was also proposed. The proposed approach was evaluated using experimental measurement.

### 1.4 Thesis Organization

The rest of the thesis is organized as follows.

Chapter 2 presents a comprehensive review of existing literature. It starts with an introduction to star trackers. The architecture, operating principle and major design specifications of star trackers are discussed. Next, a brief review of CMOS image sensors is presented and earlier works looking into radiation effects on semiconductor devices and CMOS image sensors are described. The chapter covers the cause of radiation effects and various forms of performance degradation due to those effects. Finally, existing high dynamic range CMOS image sensor solutions are presented, categorized and explained, with some examples from literature.

Chapter 3 is dedicated to radiation-tolerant pixel design. The design details of four radiation-tolerant pixels are described. Different pixel performance parameters such as dark current, dark current non-uniformity and temporal noise are analyzed using radiation characterizations. A radiation-tolerant image sensor based on the characterization results is briefly presented.

Chapter 4 introduces the operating principle, architectural design, circuit details, simulation results and chip measurement of two wide dynamic range CMOS image sensor architectures. The first focuses on the concept of adaptive integration time and the second

is based on a CTIA pixel and a charge subtraction scheme which combines high sensitivity with high dynamic range.

Chapter 5 introduces a smart CMOS measurement sensor for star centroiding. The proposed sensor architecture integrates a focal-plane SNR improvement algorithm to improve centroiding accuracy. The sensor architecture, circuit design considerations, proof-of-concept implementation and measurement results are described.

Chapter 6 draws some conclusions and suggests future work.

### Chapter 2

## Background Study and Literature Review

This chapter conducts a background study and provides a detailed review of related works in literature. It starts with an introduction to star trackers, focusing on the design specification and accuracy qualification of a star tracker with regard to the sensor employed. It then outlines several design challenges that a CMOS image sensor has to address if it is to be used in star trackers. The analysis shows how, just like other space electronics, star tracker sensors must have radiation tolerance as a common qualification. They must also have high sensitivity and wide dynamic range to achieve high tracking accuracy. After a brief introduction to CMOS image sensors, a detailed description of radiation effects on CMOS devices is presented, followed by a review of general radiation hardening design techniques. With regard to high dynamic range CMOS image sensors, several representative high dynamic range CMOS image sensor solutions described in literature are categorized and discussed.

### 2.1 Attitude Determination of Satellites

Attitude determination is the process of estimating satellite orientation by observing others celestial objects or reference points remotely. Commonly used reference objects

are the Earth magnetic field, the Sun, the Earth and celestial sphere and stars. Satellite attitude is determined based on the calculation of its relative attitude to these well-known objects in space. It is also controlled to point to some orientation for the purpose of performing specific operation during space mission, for example, pointing solar panels at the sun, pointing a high-gain communications link towards a ground station or attitude acquisition for a scientific payload. Based on different aspects of requirements, such as pointing accuracy, space constraints and power consumptions, the on-board attitude determination and control system (ADCS) is equipped with suitable sensor configuration [10]. Commonly used attitude sensors are sun sensor, magnetometer, gyroscope, earth horizon sensor, star tracker, etc.

#### 2.1.1 Sun Sensor

The sun sensor is the most widely used sensor type on satellite due to simple structure, low cost, and low power consumption [11] [12]. It is a device to measure the sun illumination using a photodiode to estimate incident angle of the sun rays relative to the sensor [13]. Sun being the brightest light source in space around the earth, the sun sensor is a reliable sensor without discriminating among sources [14]. There are numerous types of sun sensor in the market with field of view ranging from 10 degrees to 128 degrees and accuracy from 0.5 degrees to 5 degrees [15] [16] [17].

### 2.1.2 Magnetometer

Magnetometer is an instrument to measure the strength or direction of magnetic fields. The earth magnetic field is modeled to have moderate accuracy using state-of-the-art earth magnetic field models. There are many types of magnetic sensor: search coil, fluxgate, optically pumped, nuclear precession, SQUID, Hall-effect, anisotropic magneto resistance and micro-electro-mechanical systems (MEMS)-based magnetic sensors [18]. They vary in mass, sensor complexity and power consumption [19].

#### 2.1.3 Gyroscope

Gyroscope is an instrument used to measure the rotational rate [20]. There are various types of gyroscopes, such as mechanical, optical, MEMS and etc. They differ in operation principles. The gyroscope axes are aligned with the satellite body frame [21]. The gyroscope is often used with other sensors. For instance, an inertial measurement unit (IMU) is an integrated electronic device with a 3-axis magnetometer, a 3-axis gyroscope and a 3-axis accelerometer. It can achieve a reasonable accuracy.

#### 2.1.4 Earth Horizon Sensor

Earth horizon sensor is an infrared device that detects the contrast of the cold space and the earth surface and determines orientation relative to the infrared radiation from earth surface. They can also provide moderate accuracy at a low cost [22]. The disadvantage is that this type of sensor is restricted to the circular orbit.

#### 2.1.5 Star Tracker

Star tracker is an optical-electronics device that determines the satellite attitude by measuring starlight directions. Starlight directions are fixed in the inertial reference frame (ECI frame) [23], and starlight directions are known to be extremely accurate. Therefore, the accuracy of star trackers can be in range of arc seconds. It is the most accurate solution among all the state-of-the-art attitude sensors.

Star tracker in old generations are expensive, bulky and power thirsty until the era of solid-state imaging [24]. Current generation star trackers widely use CMOS image sensors as their sensing components. The development in star trackers benefits from the advantages of CMOS technology, such as low power, low cost and capability of system-on-a-chip (SoC) integration. It allows star trackers to become smaller and lighter, making it the best candidate for miniaturized space platform. The SoC integrability also enables the

great advancement in the efficiency of the data processing. Traditionally, data must be transmitted to ground and the attitude determination is performed in the ground station after downloading star image data through telemetry. Modern star trackers integrate a signal processing microprocessor in it so it can perform attitude determination algorithms such as image processing, star identification and attitude calculation directly on board. A fast update rate up to 100 Hz can be achieved.

### 2.2 Review of Star Trackers

#### 2.2.1 Overview

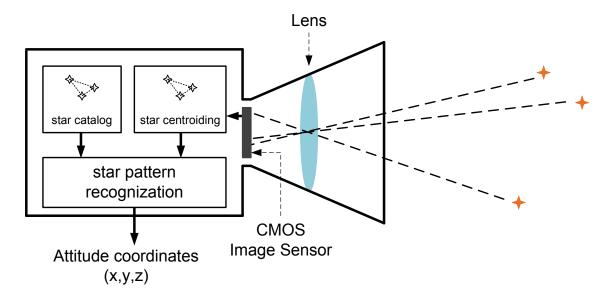

Fig. 2.1 shows the block diagram for a typical star tracker. The device mainly consists of a set of telescope optics and an image sensor together with signal processing electronics [25].

Figure 2.1: System block diagram of a typical star tracker.

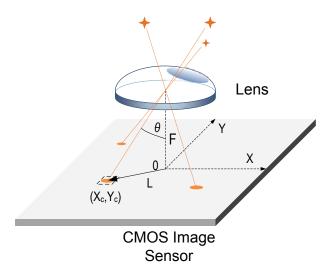

The optical system and the CMOS image sensor map the star field onto the focal plane, as shown in Fig. 2.2. The centroids of the detected stars are extracted and computed to build up a star pattern after necessary star image processing. On the focal

plane, the positions of the star centroids are transformed into a Cartesian coordinate system using a pinhole model. Star catalog is a database which lists the stars used for star pattern recognition. Usually, it requires to be processed before it is loaded into the star tracker's on-board memory [26]. A subset of the star catalog is often selected in consideration of database size and searching speed. The star pattern recognition takes the calculated star centroids as input and extracts important star features following the recognition algorithm. It then searches to match the star pattern with the reference patterns in star catalog, identify the pattern and produce the attitude coordinates. There are different autonomous star pattern recognition algorithm and they vary in complexity, recognition speed, database size, recognition accuracy, and recognition robustness.

Figure 2.2: Focal plane for star centroid calculation.

In a star tracker, there are two operating scenarios: initial attitude estimation mode (or "lost in space" mode) and attitude tracking mode. In the initial attitude estimation mode, the star tracker has no pre-knowledge of the attitude information. It requires to perform star pattern recognition as discussed. The identification typically takes a few seconds to complete. This mode is used in the launch and early orbit phase (LEOP) of the satellite or employed when the satellite losses its attitude. The attitude tracking

mode is used when the star tracker has already known its three axis attitude with some uncertainties. The task in this mode is much easier since only previously identified stars at known positions needs tracking.

#### 2.2.2 Star Detection and Star Centroiding

Stars are point sources and the most accurate optical references for satellite attitude determination. The stars positions are fixed in the Earth center inertial frame and they are very small size objects as seen from the solar system. The star catalog contains the star positions in arc-seconds accuracy. Hence, the star tracker can perform the attitude determination with accuracies in the arc-seconds range. Due to the imperfection of star tracker hardware such as optical lens, image sensor and electronic circuitry, the practical accuracy is estimated around 90 arc-seconds.

For an aberration-free lens system, the point spread function (PSF) on the focal plane obtained by far-field diffraction analysis is usually a Bessel function. However, the energy distribution of star image will not be a Bessel function as the effects of the aberration and defocusing. Generally, the defocused starlight is assumed to have a two-dimensional Gaussian distribution [27], a common assumption in optical applications with point sources:

$$I(x,y) = \frac{I_0}{\sqrt{2\pi\sigma_{PSF}^2}} \exp\left\{-\frac{(x-x_c)^2 + (y-y_c)^2}{2\sigma_{PSF}^2}\right\}$$

(Eq. 2.1)

where  $(x_c, y_c)$  represents the position of the "true" star center,  $I_0$  is the starlight intensity and  $\sigma_{PSF}$  is the spread of the Gaussian. Due to the discrete pixelization on the focal plane, the two-dimensional bell-shaped responses will typically spread over several neighboring pixels with peak in the center and form a star spot. By calculating the centroid of the star spot using hyperacuity technique or centroiding algorithm, the accuracy of the star position can achieve sub-pixel accuracy, and thus the attitude can achieve arc-seconds accuracy.

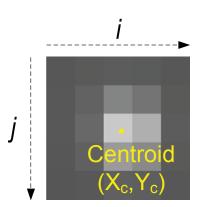

The most common centroiding algorithm to determining the star locations is the center of mass (COM) algorithm [28]. There are a few other variants of the algorithm but bear the same principle. In this algorithm, every pixel in the image and compares it to a threshold value. If a pixel is above the threshold, a square region of interest (ROI) is identified with the detected pixel at the center. The pixel values on the ROI border are averaged and subtracted from each pixel within the ROI. This process subtracts out the background noise. A COM calculation is then used to find the centroid location within the ROI.

Figure 2.3: An example ROI with  $5\times5$  pixels. The highlighted centroid is calculated using the centre of mass algorithm. It can achieve sub pixel accuracy

Fig. 2.3 shows an example pixel responses in a  $5\times5$  region-of-interest (ROI). The star centroid can be calculated as follows:

$$\begin{cases} x_c = \sum_{i,j} x_{ij} S_{ij} / \sum_{i,j} S_{ij} \\ y_c = \sum_{i,j} y_{ij} S_{ij} / \sum_{i,j} S_{ij} \end{cases}$$

(Eq. 2.2)

where  $(x_c, y_c)$  represents the calculated centroid coordinate and  $S_{ij}$  is the signal magnitude at pixel(i,j) in the ROI. The error introduced by the centroiding algorithm has a

systematic contribution and a random one [29]. Systematic error is due to the nature of the algorithm, for example the assumptions of point spread function or the effects of pixelization and spot size. On the other side, random contribution comes from the measurement uncertainty. The deviation of  $S_{ij}$  due to sensor noise from its ideal value will propagate through a deviation in the calculated centroid [30]. In [31], the effects of various noise sources of CMOS image sensors on the centroiding accuracy were analyzed in detail. It is suggested the centroiding accuracy can be improved with the increase of SNR.

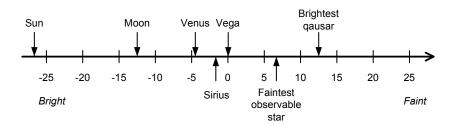

### 2.2.3 Apparent Magnitude

One of the fundamental observable quantity of a stellar object is its brightness. Because stars can have a very wide range of brightness, it is a common practice to introduce a scaled system to classify the brightness. Historically, the magnitude scale is the logarithmic measure of the brightness of an object, in astronomy, measured in a specific wavelength or passband, usually in optical or near-infrared wavelengths. The apparent brightness of a star observed from the Earth is hence called the apparent magnitude. Fig. 2.4 shows the apparent magnitude of some exemplary celestial objects along the magnitude scale. The most negative value on the ruler represents the brightest celestial objects and the faintest on the other side. Most stars stay in bounds of magnitude 1 to 6. Some very bright celestial objects can have magnitudes of negative numbers and very faint objects that cannot be detected by human eyes have magnitudes greater than +6. Some example apparent magnitudes are: Sun = -26.7, Moon = -12.6, Venus = -4.4, Sirius = -1.4, Vega = 0.0, faintest naked eye star = +6.5, brightest quasar = +12.8 and faintest object = +30 to +31.

On this quantified magnitude scale, a magnitude interval of 1 corresponds to a factor of  $100^{1/5}$  or approximately 2.512 times the amount in actual light intensity. And an

Figure 2.4: Apparent magnitude of some celestial objects in the magnitude systems.

increase of 1 in the magnitude scale corresponds to a decrease in brightness by such factor. Therefore, the calculation between any two magnitudes can be performed by raising or the 2.512 to the power of the number equal to the difference in magnitudes. In general, the intensity-magnitude relation between two stars is mathematically given in Eq. 2.3 and in Eq. 2.4 reversely.

$$m_2 - m_1 = -2.5(\log_{10} I_2 - \log_{10} I_1) = -2.5\log_{10}\left(\frac{I_2}{I_1}\right)$$

(Eq. 2.3)

and

$$\frac{I_2}{I_1} = 100^{\frac{m_1 - m_2}{5}} = 2.512^{(m_1 - m_2)}$$

(Eq. 2.4)

where  $m_1$  and  $m_2$  are apparent magnitudes to both stars belong, respectively, and  $I_1$  and  $I_2$  are the corresponding intensity. This relation indicates, for instance, first magnitude stars are about  $2.512^{2-1} = 2.512$  times brighter than second magnitude stars, and  $2.512^{3-1} = 2.512^2$  times brighter than third magnitude stars, etc. The knowledge is further used to calculate the star light sensitivity if the intensity of one celestial object is already known, the intensity of other one can therefore be determined by this magnitude mapping. In next section, the star light sensitivity are calculated following this manner with apparent magnitude taking the Sun as a reference magnitude point.

#### 2.2.4 Star Light Sensitivity

Knowing the apparent magnitudes of two celestial bodies, one can identify the illumination intensity of the star given the illumination intensity of a reference celestial body. Since many bright stars in the star field have surface temperatures close to that of the Sun and therefore belongs to the same spectral class G2. The calculation can be easily done from the above relation. The following calculation is adapted from [1]. As a reference, the apparent magnitude (Mv) of the Sun is -26.7 and the solar flux is 1.3 KW/m<sup>2</sup>. Therefore the Sun is  $2.512^{26.7}$  times brighter than a  $M_v = 0$  star. The incident power on an imaging area of 1mm<sup>2</sup> from  $M_v = 0$  star regarded as a black body radiator shares the same relative spectral characteristic and the total power is then  $(1.3 \text{ KW/m}^2 \times 10^{-6}\text{m}^2)$ /  $2.512^{26.7} = 2.96 \cdot 10^{-14} \text{ W}$ .

This calculated power received from a black body is spread over the total spectral range and is a function of the wavelength and temperature, which is given by

$$I(\lambda, T) = \frac{2 \cdot \pi \cdot h \cdot c^2}{\lambda^5 \cdot (e^{h \cdot c}/\lambda \cdot k_B \cdot T - 1)}$$

(Eq. 2.5)

where  $\lambda$  is the wavelength and T is the temperature (in Kelvin). Other constants are  $h = 6.626 \cdot 10^{-34} \text{ J} \cdot \text{s}$ ; c is the speed of light equal to  $2.997 \cdot 10^8 \text{ m/s}$ , and  $k_B$  is Boltzmann constant equal to  $1.38 \cdot 10^{-23} \text{ J/K}$ . The resulting total power influx from a  $M_v = 0$  star with 5800K temperature on an area of 1mm<sup>2</sup> is shown in Fig. 2.5 (a).

Of the total amount power received, the portion of the wavelengths that can reach the focal plane is limited by the optics. As the the optical system transmits visible wavelengths in the range between 400 nm to 800 nm band. This, in fact, is like a passband filter and the resulting power influx on the focal plane is shown in Fig. 2.5 (b). Moreover, it is possible to express the power influx in term of photon influx due to the energy of a photon  $E = hc/\lambda$ . The resulting spectral spread is shown in Fig. 2.5 (c).

Figure 2.5: (a) Power spectrum from a  $M_v = 0$  star on an area of 1mm<sup>2</sup>. (b) Power influx onto the focal plane. (c) Photon influx onto the focal plane. (d) Detectable photons on the focal plane. Adapted from [1].

On the focal plane, these photons are converted into photo-generated charges (photoelectrons). Only a fraction of these photons are effectively converted and contribute to the signal due to the quantum efficiency limitation. The limitation is wavelength dependent. The resulting photons received in a typical sensor is as shown in Fig. 2.5 (d). The total amount of photoelectrons that are summed over the wavelength is 19100. This means that under one second exposure and a lens aperture area on 1mm<sup>2</sup> will generate 19100 photoelectrons for a  $M_v = 0$  star. Using this number, it is easy to calculate other

stars with other magnitudes. Take  $M_V = 4$  star as example, the resulting photoelectrons generated in 1mm<sup>2</sup> under 200ms exposure time will eventually be equal to

$$19100 \frac{photoelectrons}{s \cdot mm^2} \cdot \frac{1}{2.512^{4-0}} \cdot 0.2s \cdot \pi \cdot 15^2 mm^2 = 68000 \frac{photoelectrons}{mm^2} \quad \text{(Eq. 2.6)}$$

This example of calculation gives a quantitative estimate of the star signals in a star image. Generally, a star can only generate limited number of photoelectrons, which makes star detection a challenging issue. At one hand, a detection threshold is necessary which sets a boundary to differentiate the real stars from the dark background. The background quality of the captured images are typically limited by several sensor noise contributions. To avoid false detection, the signal charges should be sufficiently large to achieve a large signal-to-noise ratio (SNR). When selecting the detection threshold, one should take into consideration of acceptable SNR.

On the other hand, when above the detection threshold, a broad range of apparent magnitudes are required to be detected without losing the capability to differentiate their apparent magnitude. This requires the image sensor to support a high dynamic range capability to capture all illumination details within star pixels. Any loss of illumination information by saturation is not expected. The illumination details within the star pixels are critical to the further star centroiding processing.

### 2.2.5 Star Catalog and Star Pattern Recognition

Star catalog is a star database that lists stars with identifications. It is used for initial attitude acquisition or for calculating the attitude quaternion. There are a number of available open-source star catalogs, such as SAO J2000. Modern autonomous star trackers have an on-board star catalog stored in the firmware. The star catalog needs a delicate compilation process before installed to the firmware [32]. Typically, it is subsetted

Table 2.1: Star Radiation and Luminance

| Light source     | Apparent magnitude | Radiation( $W/m^2$ ) | Luminance(lux) |

|------------------|--------------------|----------------------|----------------|

| Sun              | -26.7              | 1360                 | 130000         |

| Earth            |                    | 193                  | 3.15193e+4     |

| Sirius           | -1.4               | 5.19e-8              | 1e-5           |

| Star Magnitude 0 | 0                  | 1.44e-8              | 2.7e-6         |

| Star Magnitude 1 | 1                  | 5.7716e-9            | 1.0533e-6      |

| Star Magnitude 2 | 2                  | 2.3105e-9            | 4.2131e-7      |

| Star Magnitude 3 | 3                  | 9.2418e-10           | 1.6852e-7      |

| Star Magnitude 4 | 4                  | 3.6967e-10           | 6.74e-8        |

| Star Magnitude 5 | 5                  | 1.4787e-10           | 2.6964e-8      |

| Star Magnitude 6 | 6                  | 5.9148e-11           | 1.0785e-8      |

from the complete catalog according to the spectral sensitivity of the star tracker. It is further used to generate star pattern database, which stores the features-in-interest describing each reference star in this catalog.

Star pattern recognition is to extract these important features of captured star and match them with the database according to some rules. There are different recognition algorithms developed, which vary in complexity, recognition speed, database size, recognition accuracy and robustness [33]. One well-established method is Liebe algorithm [28] [34]. The method utilizes triple star pattern, characterized by three features, namely 1) the angular distance to the first neighbour star; 2) the angular distance to the second neighbour star; and 3) the spherical angle between the two neighbour stars. This triple star pattern is compared with the pattern catalog to determine the correct star identity. Other algorithms include grid star pattern recognition algorithm [35] [36], pyramid star pattern recognition algorithm [37], the planar triangle algorithm, geometric voting algorithm [38] and so on.

# 2.3 Fundamentals of CMOS Image Sensors

There are two major competing technologies for solid-sate imaging in the market: charge coupled devices (CCD) and CMOS image sensors (CIS). The introduction of first CMOS image sensors by Westinghouse, IBM, Plessy and Fairchild dates back to late 1960s [39]. CCDs were invented by Bell Laboratory as an analog memory device in 1970 and quickly became the dominant technology in the field of solid-state imaging. Early CMOS image sensors are severely limited by CMOS technologies available at that moment. They suffer from poor imaging performance and large pixel size, which constrain their applicability to low-end imaging applications. Since 1990s, CMOS image sensors have been the subject of extensive development after the emergence of Active Pixel Sensor (APS) and the advent of deep submicron CMOS technologies. Thanks to the rapid advancement of CMOS imaging technologies in last decades, the imaging performance was drastically improved, making CMOS image sensors a viable alternative to CCDs in a wide range of applications. In addition, many advantages of CMOS image sensors such as low power, low cost due to standardized fabrication process and the inherent capability to integrate signal processing on-chip with image capturing has found its usefulness in many emerging applications [40], including space applications.

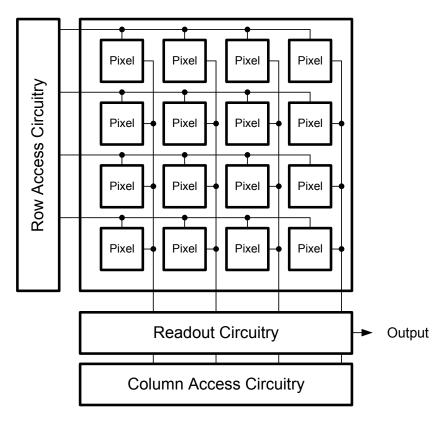

### 2.3.1 Imager Architecture

Generally, a CMOS image sensor is composed of an imaging area and peripheral readout circuitry, as shown in Fig. 2.6. The imaging area consisting of a two-dimensional array of pixels is the core of the imager and the pixel is the key device that is responsible for the imaging performance. Row and column access circuits are used to select a pixel in the array and read the pixel value. These can be either scanners for sequential readout or decoders that enable random access to the pixel in the array. There is another category of event-driven readout method, called Address Event Representation (AER).

AER is originally a communication protocol of communicating sparse neural events between neuromorphic chips. Therefore, AER is commonly used in bio-inspired imaging systems [41] [42] [43]. Instead of reading out the pixel values passively driven by the sensor controller, the readout process is initiated by the pixel itself by sending a request once an event is "fired". An acknowledgement is sent back by the global AER controller. The handshaking between the pixel and the outside is established and the data transmission is initiated. When there are multiple requests at the same time, row and column arbitrated circuits are then required to ensure multiplexing the 2D array into a single output bus. The readout circuitry is composed of an one-dimensional array of signal processing circuits. They can vary in different forms, such as sample and hold circuit, noise cancelling circuits and column-parallel ADCs and so forth.

Figure 2.6: General architecture of a CMOS image sensor.

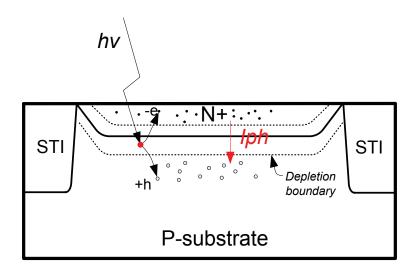

### 2.3.2 Photodetection and Photodetectors

Most photodetectors in solid-state imaging are essentially reversed-biased PN junctions. The most popular type of photodetector used in CMOS image sensors is photodiode (PD). It is easy to fabricate in bulk CMOS process. There are a variety of photodetectors based on the structure variations and operation principles. Other photodetectors include photogates, phototransistors, avalanche photodiodes (APDs) and single photon avalanche diodes (SPADs). In the following discussion, photodiode is used to explain the photodetection.

Fig. 2.7 shows the cross-section view of a N+ diffusion/P-substrate junction photodiode. Other commonly-used photodiodes are N-well/P-substrate and P+ diffusion/N-well photodiodes [44], etc.

Figure 2.7: Cross-section view of a N+ diffusion/P-substrate photodiode.

When light passes through the dielectric layers and is incident on silicon, a portion of the incident light is reflected but the rest will penetrate into the silicon and is absorbed in the material. The penetration depth depends on the light wavelength. Typically, blue light penetrates about 0.2  $\mu$ m while red light penetrates as deep as 10  $\mu$ m. The differ-

ence in penetration depths can be an important figure for determining the photodiode structure for the design of color sensors.

When light is absorbed in silicon, photons carrying energy  $(E = h\nu = hc/\lambda)$  above bandgap  $(E_g = 1.124)$  of the silicon material can excite an electron to conduction band, leaving a hole in the valance band. The process is called electron-hole pair (EHP) generation. When EHP generation occurs in the depletion region of the photodiode, the electrical field will sweep electrons to N+ diffusion and holes to P substrate, respectively. The photogenerated carriers are effectively separated by the electric field. The movement of a large amount of photogenerated carriers forms the flow of drift current. If EHP is generated outside the depletion region where the electric field is weak, the carriers are likely to recombine. But there is still chance that they can diffuse to the depletion region and get separated. This small diffusion current also contributes part of the photocurrent  $(I_{PH})$ . The photogenerated electrons will be collected in the N+ diffusion. Considering all the above conditions, the carrier collection is a complex mechanism related to a number of factors including the location and width of the depletion region, minority carrier diffusion length. These, in turn, are primarily determined by the doping profile of the photodiode and strongly influenced by the process parameters.

It can be estimated that for typical ambient illumination level of approximately several hundred lux, the photocurrent is as small as on the order of a few picoamperes. It is difficult to measure and read photocurrent directly. Therefore, a practical image sensor must accumulate the charges over some time so that a reasonable signal can be measured. The time required to accumulate the charges is often referred to integration time or exposure time. The sensor is often referred to voltage mode or integration mode sensor. In such mode, N+ diffusion of the photodiode is electrically floated when the photocurrent discharges the parasitic capacitance of the photodiode. One can measure the voltage drop so at to determine the photocurrent from simple electric relationship. One thing to note

is that the discharge of the photodiode is not perfectly linear. The nonideality is caused by the change of the deletion width and thus photodiode capacitance due to the drop of the reversed-bias voltage.

#### 2.3.3 Basic Pixel Architecture

The photodetector, together with accessing and readout circuits, comprises a pixel. There are different types of pixel architectures in CMOS image sensors.

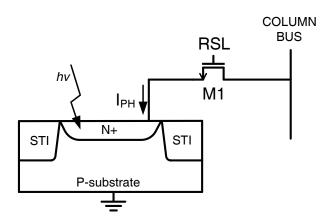

#### 2.3.4 Passive Pixel Sensor

The first commercially available CMOS pixel sensor in history is Passive Pixel Sensor (PPS). PPS has a simple structure. It is composed of a photodiode and a switch transistor, as shown in Fig. 2.8. It is similar to dynamic random access memory (DRAM).

Figure 2.8: Schematic and cross-section view of a PPS.

Its simple structure of PPS has the advantage that the pixel area consumed by the circuits is minimized. This allows it to achieve high fill factor, which is preferable in CMOS image sensors. But the simplicity is also the source of several disadvantages. Switching noise and SNR is the crucial issue. Specifically, the noise power in charges is kTC, where C is the parasitic capacitance on the column bus. One should note that the

parasitic capacitance on the column bus scales up when the array size grows. This results in a large sampling capacitance for a PPS and hence results in large noise. In addition, as the parasitic capacitance on the column bus is large, the small amount of charges in PPS cannot change the voltage much. The output signal degrades easily, making SNR a significant issue during readout.

#### 2.3.4.1 3T Active Pixel Sensor

Active Pixel Sensors (APS) is named after its active device amplifiers the signal in each pixel to distinguish from the name of PPS. There are a number of advantages compared with PPS, which makes it the most popular pixel architectures. Fig. 2.9 shows the schematic of an APS. The pixel configuration is referred as 3T APS. Another advanced 4T-APS has four transistors is discussed in the next section.

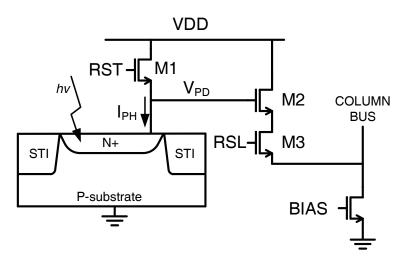

Figure 2.9: Schematic and cross-section view of a 3T APS

The pixel has a photodiode and three NMOS transistors. M1 is used to reset the photodiode to a reset voltage level, which is typically,  $VDD - V_{TH}$ , where  $V_{TH}$  is the threshold voltage of M1. After M1 turns off, the cathode of the photodiode, which is the sensing node is then electrically floating. The photocurrent, normally ranging

from femtoampere to picoamperes, starts to discharge the photodiode. The accumulated charges change the potential on the sensing node and the voltage of the photodiode  $V_{PD}$  decreases according to the input light intensity throughout the integration period. M2 acts as a source follower when row select signal RSL is asserted to turn on M3. The current source of the source follower resides in the column and is shared by all pixels in a column. The signal is buffered to the column bus. When the pixel readout is complete, RSL is turned off and RST is turned on to repeat the above procedures. Noteworthy is that 3T APS readout is nondestructive so multiple sampling on the sensing node is allowed.

While the accumulated charges are transferred directly to the column bus in a PPS, an APS converts the accumulated charges to a voltage signal. By incorporating amplification inside the pixel, the APS effectively reduces readout noise at a cost of lowering the fill factor. Also, fixed pattern noise (FPN) is introduced due to the amplifiers but can be significantly reduced in column signal processing [45].

Despite the SNR advantage of APS over PPS, there are several issues with the APS. It is difficult to suppress the reset noise, i.e. kTC noise due to the reset transistor. Besides, the photodetection and the photoconversion (from accumulated charges to voltage) on the same node constraints the photodiode design. The full well capacity increases as the photodiode parasitic capacitance increases. On the other hand, the conversion gain is inversely proportional to this capacitance. These two parameter, in turn, affects other important APS performance figures, that is, dynamic range and sensitivity. This implies the trade-off relationship existing in a 3T APS. The 4T APS resolves the trade-off as well as cancel easily suppress the kTC noise.

#### 2.3.4.2 4T Active Pixel Sensor

The 4T APS has been introduced and developed based on 3T APS and to alleviate the aforementioned problems with the 3T APS.

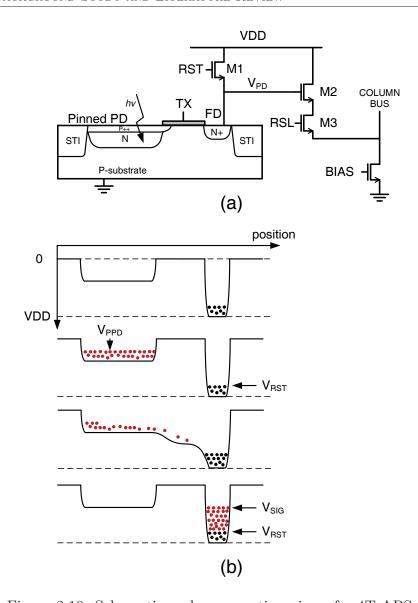

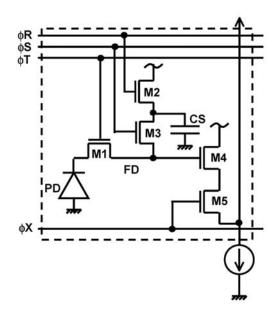

Figure 2.10: Schematic and cross-section view of a 4T APS.

The schematic of a 4T APS is shown in Fig.2.10 (a). In a 4T APS, the site of photodetection and photoconversion are separated by an additional transistor, TX. Photodetection is conducted within the pinned-photodiode (PPD) and the accumulated charges are transferred to a floating diffusion (FD) and converted to a voltage. The cross-sectional view of this region is illustrated in the figure. PPD is a specialized photodiode structure based on conventional photodiode. In contrast to the conventional PD, there is a very

thin pinning P++ layer on top of the PN junction, hence forms another PN junction close to the silicon surface. There are advantages with this structure. Firstly, PPD demonstrates a better light sensitivity than conventional photodiode since another PN junction on top of the N region extends the depletion region to the surface, which enables the effective carrier collection generated by short wavelength photons. Moreover, the pinned layer isolates N region from the defective Si/SiO2 interface so as to reduce the dark current generated from the interface states. However, the fabrication of PPD requires the support of specialized CMOS image sensor process, which is more expensive than standardized CMOS process. Many CMOS image sensor process are developed from mixed-signal CMOS process and offered as an additional process option in many foundries.

The 4T APS can achieve low noise readout and provides the imaging performance comparable to CCDs. A proper timing can be devised together with the use of charge transfer characteristics to supress kTC noise. The pixel operation procedure is illustrated with the help of potential diagram [46], as shown in Fig. 2.10. It is assumed that in the reset phase, there are no accumulated charges in the PPD, thus the PPD is completely depleted. The photogenerated charges are accumulated in PPD when the FD is reset by turning on the the reset transistor M1. The reset level,  $V_{RST}$  is read out firstly by turn on the row select switch M3. After the reset readout is complete, the charges in PPD is then transferred to the FD by turning on the transfer gate TX, followed by the signal readout ( $V_{SIG}$ ). It can be noted the voltage difference between the reset level and the signal level is strictly proportional to the amount of accumulated charges in PPD. The readout of both reset level and are short enough in time, which is essential for correlated double sampling (CDS) to cancel the kTC noise in column signal processing.

A carefully designed potential profile in PPD, FD and the transfer gate is required to assure a complete depletion in PD as well as a complete charge transfer through TX.

### 2.3.5 Performance Analysis

There are a number of important features and characteristics used to describe the performance of CMOS image sensors. This sections gives a detailed description.

#### 2.3.5.1 Quantum Efficiency

Quantum efficiency (QE) is one of the main characteristics to describe the photodetector performance. It is defined as the fraction of incident photon flux on the photodetector that contributes to the photogenerated charges. It is a function of wavelength (400-700 nm range of visible light for silicon) and is always less than one for the discussed photodetectors. QE is largely determined by the doping concentration of the photodetector, geometric arrangement of the photodetector, reflection of the dielectric property above the photodetector, etc.

#### 2.3.5.2 Dark Current

Dark current, also termed as dark signal, is another characteristic of the photodetector. It is the signal response when there is absence of light to the photodetector. The generation of dark current is due to thermal generation of charge carrier. They are related to many design and technology factors including the silicon defect density, the bias condition of the photodetector and operation temperature. Dark current is generated by several sources, including diffusion current, tunnel current, generation-recombination current in the depletion region, impact, ionizing current, surface leakage current due to surface states [46]. Dark current consumes the well capacity unexpectedly. It also varies with time and the pixel location, producing the temporal and spatial variation. The temporal variation contributes to the random noise while the spatial one adds to the fixed pattern noise.

#### 2.3.5.3 Fill Factor

Fill factor (FF) is a parameter related to pixel geometry. It is defined as the percentage of the photosensitive area to the entire pixel area. CCD achieves around 100% fill factor. Incorporating transistors in the pixel will inevitably reduce the fill factor. A high fill factor is generally desired to achieve. The use of microlens and back-side illumination (BSI) helps to increase the effective fill factor of modern CMOS image sensors.

#### 2.3.5.4 Temporal Noise

Temporal noise, also termed as random noise, is the variation in pixel values under same illumination from frame to frame [47]. It is independent of the pixel location in the array. There are several temporal noise sources in CMOS image sensor including photon shot noise, pixel reset noise, thermal and flicker noise in readout circuits and quantization noise in ADCs.

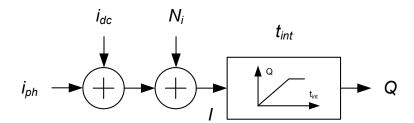

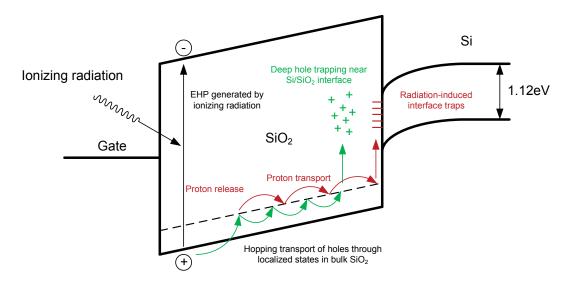

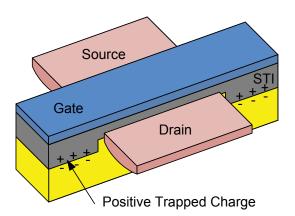

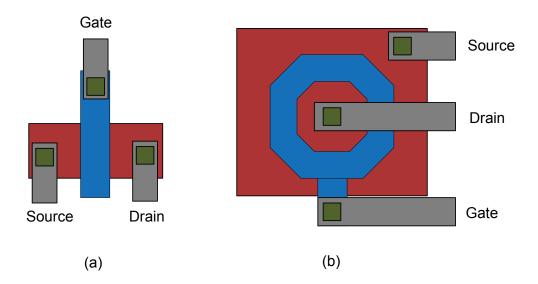

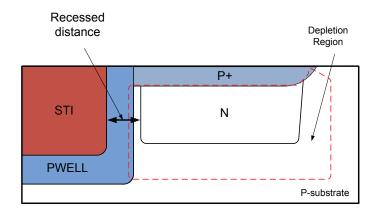

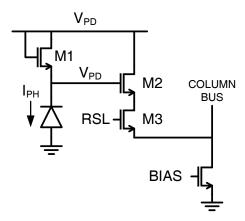

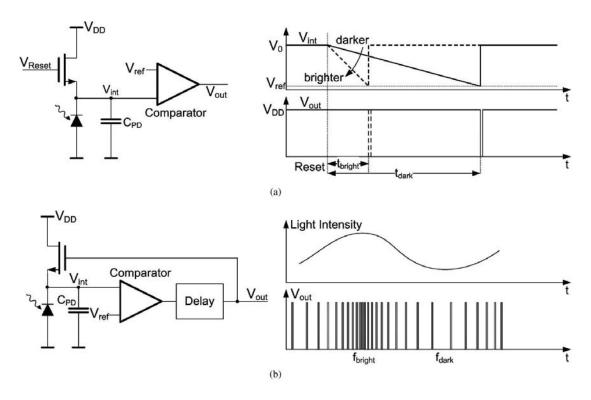

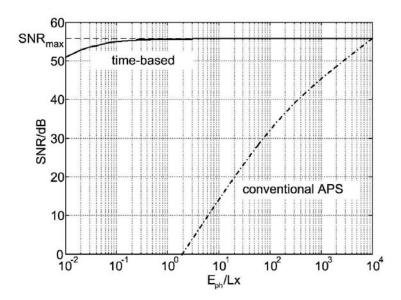

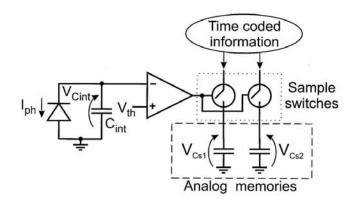

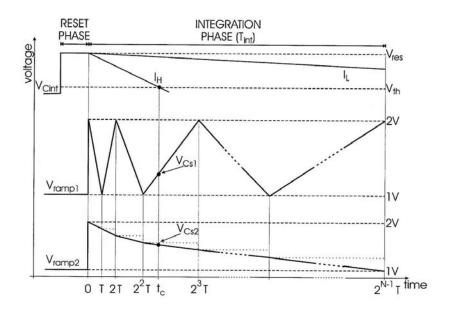

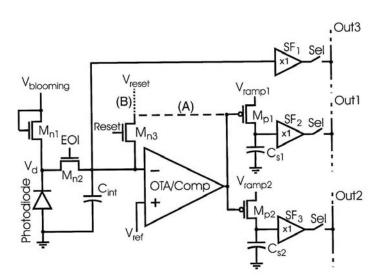

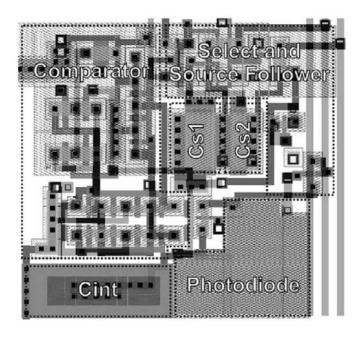

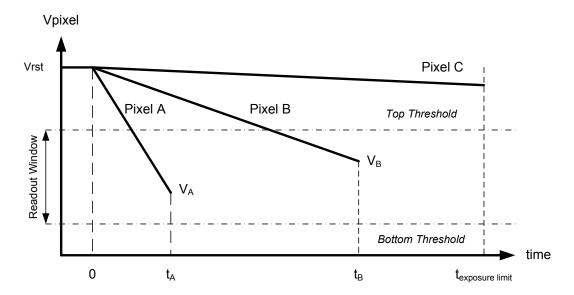

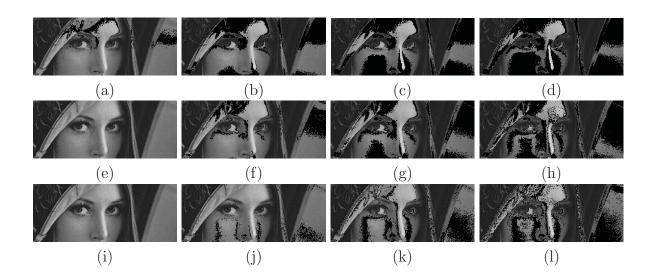

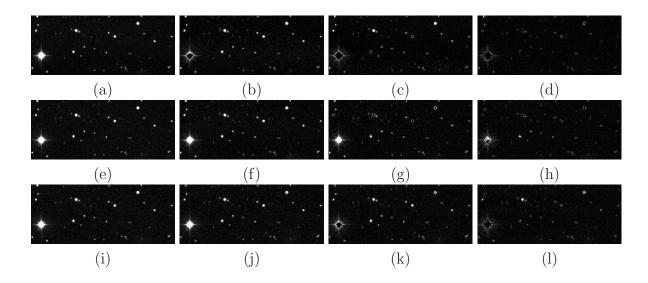

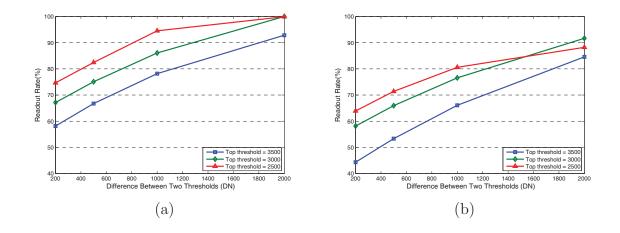

More specifically, photon shot noise is the noise associated with the random arrival of photons. It is an expression of a natural process rather than pixel design or fabrication technology. Thus, photon shot noise is the most fundamental noise among all the noise sources.